# **SIEMENS**

# **SIMATIC S5**

S5-155U CPU 948

## **Programming Guide**

This manual has the order number: **6ES5 998–3PR21**

1 Introduction User Program 3 **Program Execution** Operating Statuses and Program 4 Execution Levels 5 Interrupt and Error Diagnostics 6 **Integrated Special Functions** 7 Extended Data Block DX 0 Memory Assignment and Memory 8 Organization Memory Access Using Absolute 9 Addresses Multiprocessor Mode and Com-10 munication in the S5-155U 11 PG Interfaces and Functions 12 **Appendix** Indexes: Abbreviations 13 **Key Words**

The List of Operations, order no. 6ES5 997-3UA22, is included

with this manual.

Contents

10/98 C79000-G8576-C848 Release 04

#### **Safety Guidelines**

This manual contains notices which you should observe to ensure your own personal safety, as well as to protect the product and connected equipment. These notices are highlighted in the manual by a warning triangle and are marked as follows according to the level of danger:

#### Danger

indicates that death, severe personal injury or substantial property damage will result if proper precautions are not taken.

#### Warning

indicates that death, severe personal injury or substantial property damage can result if proper precautions are not taken.

#### Caution

indicates that minor personal injury or property damage can result if proper precautions are not taken.

#### **Note**

draws your attention to particularly important information on the product, handling the product, or to a particular part of the documentation.

#### **Qualified Personnel**

The device/system may only be set up and operated in conjunction with this manual.

Only **qualified personnel** should be allowed to install and work on this equipment. Qualified persons are defined as persons who are authorized to commission, to ground, and to tag circuits, equipment, and systems in accordance with established safety practices and standards.

#### **Correct Usage**

Note the following:

#### Warning

This device and its components may only be used for the applications described in the catalog or the technical description, and only in connection with devices or components from other manufacturers which have been approved or recommended by Siemens.

This product can only function correctly and safely if it is transported, stored, set up, and installed correctly, and operated and maintained as recommended.

#### **Trademarks**

SIMATIC ®, SIMATIC NET® and SIMATIC HMI® are registered trademarks of SIEMENS AG. Third parties using for their own purposes any other names in this document which refer to trademarks might infringe upon the rights of the trademark owners.

#### Copyright © Siemens AG 1998 All rights reserved

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

Siemens AG

Bereich Automatisierungs- und Antriebstechnik

Geschaeftsgebiet Industrie-Automatisierungssysteme

Postfach 4848, D-90327 Nuernberg

#### Disclaimer of Liability

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in this manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvementare welcomed.

© Siemens AG 1998 Subject to change without prior notice.

# **Contents**

| 1     | Introduction                                             |

|-------|----------------------------------------------------------|

| 1.1   | Area of Application for the S5-155U with the CPU 948     |

| 1.2   | Typical Mode of Operation of a CPU                       |

| 1.3   | The Programs in a CPU                                    |

| 1.4   | Which Operands are available to the User Program?        |

| 1.5   | How much Memory is available for the User Program?       |

| 1.6   | How to Tackle Programming                                |

| 1.7   | Programming Tools                                        |

| 1.8   | Converting User Programs of the CPU 928B for the CPU 948 |

| 2     | User Program                                             |

|       |                                                          |

| 2.1   | STEP 5 Programming Language                              |

| 2.1.1 | The LAD, CSF, STL Methods of Representation              |

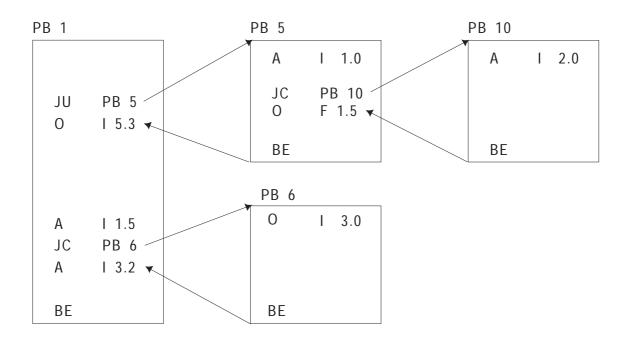

| 2.1.2 | Structured Programming                                   |

| 2.1.3 | STEP 5 Operations                                        |

| 2.1.4 | Number Representation                                    |

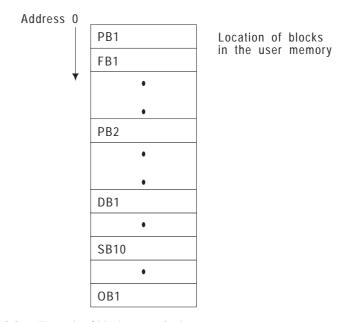

| 2.1.5 | STEP 5 Blocks and Storing them in Memory                 |

| 2.2   | Program, Organization and Sequence Blocks                |

| 2.2.1 | Organization Blocks as User Interfaces                   |

| 2.2.2 | Organization Blocks for Special Functions                |

| 2.3   | Function Blocks                                          |

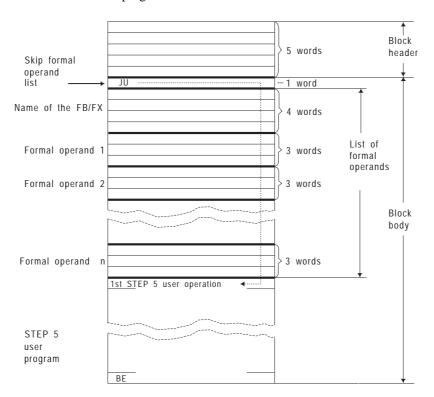

| 2.3.1 | Structure of Function Blocks                             |

| 2.3.2 | Programming Function Blocks                              |

| 2.3.3 | Calling Function Blocks and Assigning Parameters to them |

| 2.3.4 | Special Function Blocks. 2 - 33                          |

| 2.4   | Data Blocks                                              |

| 2.4.1 | Creating Data Blocks                                     |

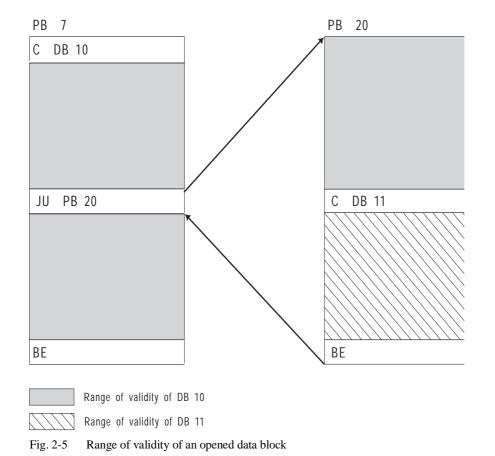

| 2.4.2 | Opening Data Blocks                                      |

| 2.4.3 | Special Data Blocks                                      |

| 3     | Program Execution                                                      | 3 - 3  |

|-------|------------------------------------------------------------------------|--------|

| 3.1   | Principle of Program Execution                                         | 3 - 4  |

| 3.2   | Program Organization                                                   | 3 - 5  |

| 3.3   | Storing Program and Data Blocks                                        | 3 - 10 |

| 3.4   | Processing the User Program                                            | 3 - 11 |

| 3.4.1 | Definition of Terms used in Program Execution                          | 3 - 12 |

| 3.5   | STEP 5 Operations with Examples                                        | 3 - 15 |

| 3.5.1 | Basic Operations                                                       | 3 - 19 |

| 3.5.2 | Programming Examples in the STL, LAD and CSF Methods of Representation | 3 - 34 |

| 3.5.3 | Supplementary Operations                                               | 3 - 49 |

| 3.5.4 | Executive Operations                                                   | 3 - 59 |

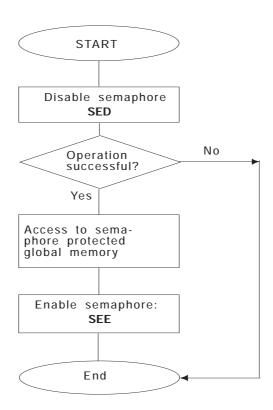

| 3.5.5 | Semaphore Operations                                                   | 3 - 75 |

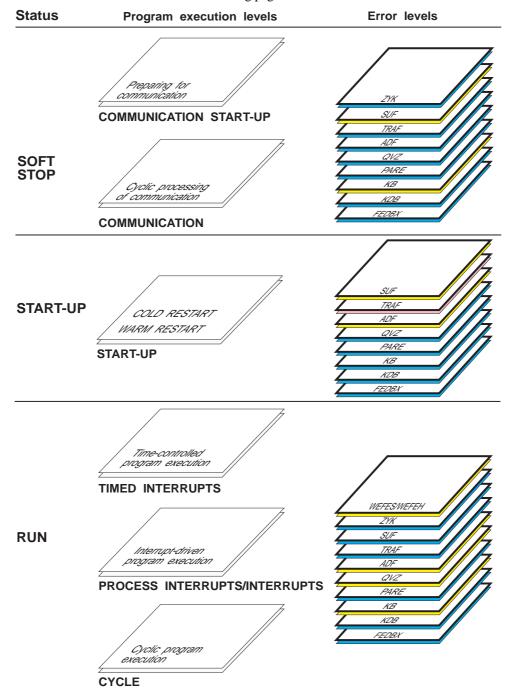

| 4     | Operating Statuses and Program Execution Levels                        | 4 - 3  |

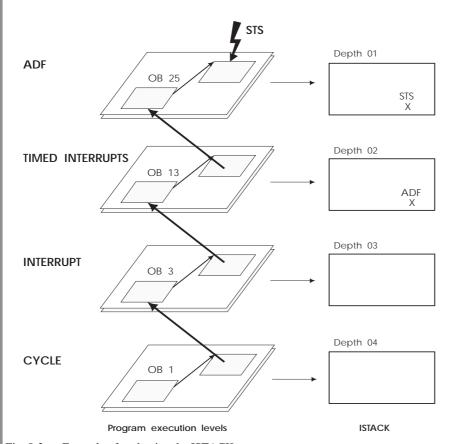

| 4.1   | Program Execution Levels                                               | 4 - 4  |

| 4.2   | STOP Mode                                                              | 4 - 9  |

| 4.2.1 | SOFT STOP                                                              | 4 - 9  |

| 4.2.2 | HARD STOP                                                              | 4 - 13 |

| 4.2.3 | OVERALL RESET                                                          | 4 - 14 |

| 4.3   | START-UP Mode                                                          | 4 - 16 |

| 4.3.1 | MANUAL and AUTOMATIC COLD RESTART                                      | 4 - 17 |

| 4.3.2 | MANUAL and AUTOMATIC WARM RESTART                                      | 4 - 18 |

| 4.3.3 | Comparison between COLD RESTART and WARM RESTART                       | 4 - 21 |

| 4.3.4 | RETENTIVE COLD RESTART                                                 | 4 - 22 |

| 4.3.5 | Comparison of COLD RESTART and RETENTIVE COLD RESTART                  | 4 - 23 |

| 4.3.6 | User Interfaces for Start-Up.                                          | 4 - 24 |

| 4.3.7 | Extended AUTOMATIC WARM RESTART with the CPU 948 (HOT RESTART)         | 4 - 27 |

| 4.3.8 | Interruptions during START-UP                                          | 4 - 28 |

| 4.4   | RUN Mode                                                               | 4 - 29 |

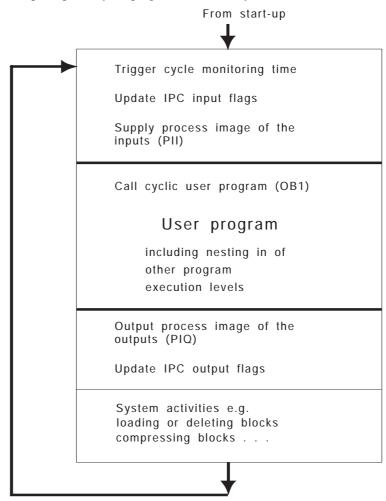

| 4.4.1 | Cyclic Program Execution                                               | 4 - 30 |

| 4.4.2 | Specifying Time and Interrupt-Driven Program Execution                 | 4 - 32 |

| 4.4.3 | Time-Controlled Program Execution.                                     | 4 - 33 |

| 4.4.4 | Interrupt-Driven Program Execution                                     | 4 - 41 |

| 5     | Interrupt and Error Diagnostics                                        | 5 - 3  |

| 5.1   | Frequent Errors in the User Program                                    | 5 - 4  |

| 5.2   | Error Information                                                      | 5 - 5  |

| 5.3   | Procedure for Error Analysis                                           | 5 - 8  |

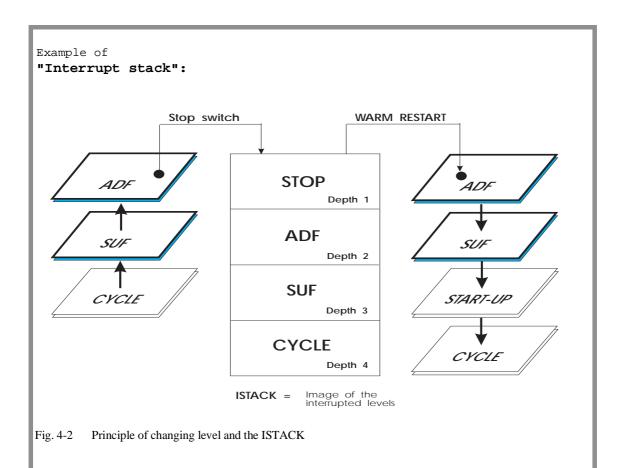

| 5.4   | Control Bits and Interrupt Stack                                       | 5 - 9  |

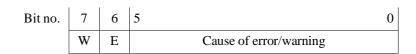

| 5.4.1 | Control Bits                                                           | 5 - 10 |

| 5.4.2 | ISTACK Content                                                         | 5 - 14 |

| 5.4.3 | Example of Error Diagnosis using the ISTACK                            | 5 - 19 |

| 5.5                                                                                      | Error Handling Using Organization Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 - 20                                                                                                     |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 5.6                                                                                      | Causes of Error and Reactions of the CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 - 23                                                                                                     |

| 5.6.1                                                                                    | OB 19: Calling a Logic Block That Is Not Loaded (KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5 - 24                                                                                                     |

| 5.6.2                                                                                    | OB 19: Calling a Data Block That Is Not Loaded (KDB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5 - 24                                                                                                     |

| 5.6.3                                                                                    | OB 23/24, OB 28/29:Timeout Error (QVZ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5 - 25                                                                                                     |

| 5.6.4                                                                                    | OB 25: Addressing Error (ADF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5 - 26                                                                                                     |

| 5.6.5                                                                                    | OB 26: Cycle Time Exceeded Error (ZYK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5 - 27                                                                                                     |

| 5.6.6                                                                                    | OB 27: (Substitution Error SUF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5 - 28                                                                                                     |

| 5.6.7                                                                                    | OB 30: Parity Error and Timeout Error in the User Memory (PARE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 - 28                                                                                                     |

| 5.6.8                                                                                    | OB 32: Load and Transfer Error (TRAF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 - 29                                                                                                     |

| 5.6.9                                                                                    | OB 33: Collision of Timed Interrupts Error (WEFES/WEFEH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 - 30                                                                                                     |

| 5.6.10                                                                                   | OB 34: Error with G DB/GX DX (FEDBX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5 - 32                                                                                                     |

| 5.6.11                                                                                   | OB 35: Communication Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5 - 32                                                                                                     |

| 5.6.12                                                                                   | OB 36: Error in Self-test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 - 33                                                                                                     |

| 5.7                                                                                      | Self-Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 - 34                                                                                                     |

| 5.7.1                                                                                    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 - 34                                                                                                     |

| 5.7.2                                                                                    | Description of the Test Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 - 35                                                                                                     |

| 5.7.3                                                                                    | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 - 37                                                                                                     |

| 5.7.4                                                                                    | Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 - 38                                                                                                     |

|                                                                                          | Internated Cuestal Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ( )                                                                                                        |

| <b>6</b><br>6.1                                                                          | Integrated Special Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                            |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                            |

| 6.2                                                                                      | OB 121: Set/Read System Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                            |

| 6.3                                                                                      | OB 122: "Disable Interrupts" On/Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |

| 6.4                                                                                      | OD 104 D 1 4 CODED 5 D1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - 11                                                                                                       |

|                                                                                          | OB 124: Delete STEP 5 Blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                            |

| 6.5                                                                                      | OB 125: Generate STEP 5 Blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6 - 17                                                                                                     |

| 6.6                                                                                      | OB 125: Generate STEP 5 Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6 - 17<br>6 - 20                                                                                           |

| 6.6<br>6.7                                                                               | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6 - 17<br>6 - 20<br>6 - 25                                                                                 |

| 6.6<br>6.7<br>6.8                                                                        | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                        | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26                                                                       |

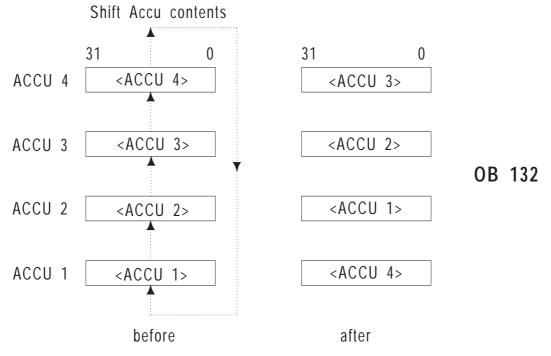

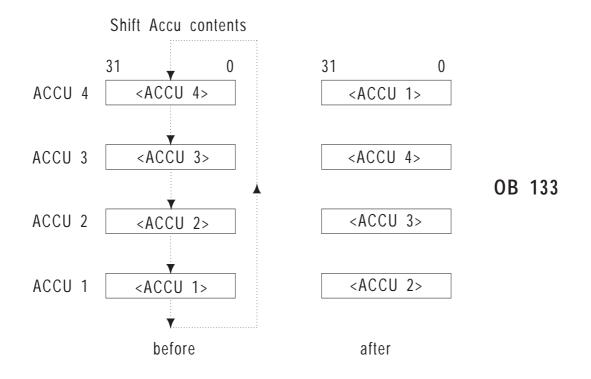

| 6.6<br>6.7<br>6.8<br>6.9                                                                 | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU                                                                                                                                                                                                                                                                                                                                                               | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27                                                             |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10                                                         | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off.                                                                                                                                                                                                                                                                                                     | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 29                                                   |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11                                                 | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off.  OB 142: "Delay All Interrupts" On/Off                                                                                                                                                                                                                                                              | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 32                                                   |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12                                         | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off.  OB 142: "Delay All Interrupts" On/Off  OB 143: "Delay Single Cyclic Timed Interrupts" On/Off                                                                                                                                                                                                       | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 29<br>6 - 32                                         |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13                                 | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off.  OB 142: "Delay All Interrupts" On/Off  OB 143: "Delay Single Cyclic Timed Interrupts" On/Off  OB 150: Set/Read System Time                                                                                                                                                                         | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 29<br>6 - 32<br>6 - 35                               |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13                                 | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU.  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off.  OB 142: "Delay All Interrupts" On/Off  OB 143: "Delay Single Cyclic Timed Interrupts" On/Off  OB 150: Set/Read System Time  OB 151: Set/Read Time for Clock-Controlled Interrupt                                                                                                                  | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 32<br>6 - 35<br>6 - 38                               |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br>6.15                 | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off.  OB 142: "Delay All Interrupts" On/Off  OB 143: "Delay Single Cyclic Timed Interrupts" On/Off  OB 150: Set/Read System Time  OB 151: Set/Read Time for Clock-Controlled Interrupt  OB 153: Set/Read Time for Delayed Interrupt                                                                      | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 32<br>6 - 35<br>6 - 38<br>6 - 43                     |

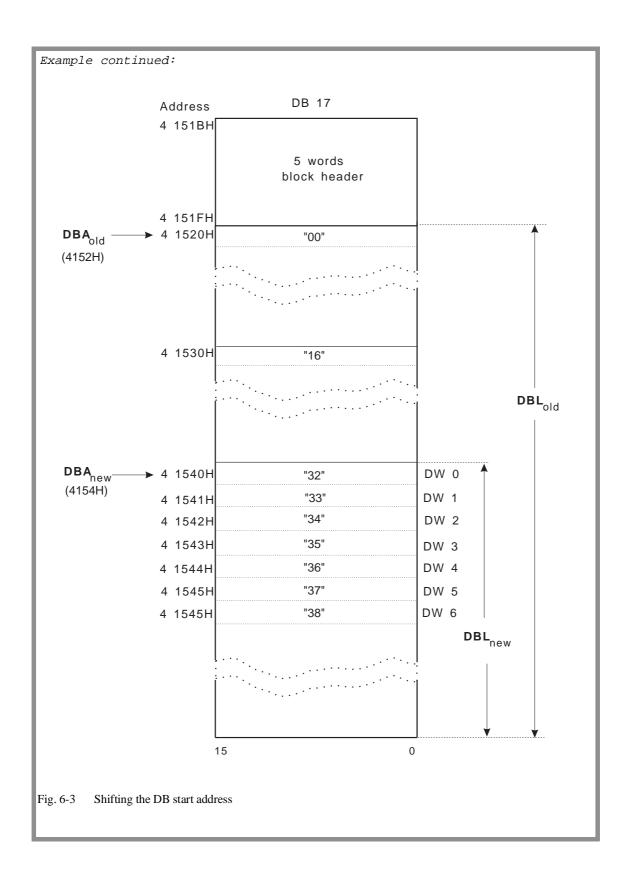

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br>6.15<br>6.16         | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off  OB 142: "Delay All Interrupts" On/Off  OB 143: "Delay Single Cyclic Timed Interrupts" On/Off  OB 150: Set/Read System Time  OB 151: Set/Read Time for Clock-Controlled Interrupt  OB 153: Set/Read Time for Delayed Interrupt  OB 180: Variable Data Block Access                                   | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 29<br>6 - 35<br>6 - 35<br>6 - 43<br>6 - 50<br>6 - 53           |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br>6.15<br>6.16<br>6.17 | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off  OB 142: "Delay All Interrupts" On/Off  OB 143: "Delay Single Cyclic Timed Interrupts" On/Off  OB 150: Set/Read System Time  OB 151: Set/Read Time for Clock-Controlled Interrupt  OB 153: Set/Read Time for Delayed Interrupt  OB 180: Variable Data Block Access  OB 181: Test Data Blocks (DB/DX) | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 32<br>6 - 35<br>6 - 38<br>6 - 43<br>6 - 50<br>6 - 53 |

| 6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br>6.15<br>6.16         | OB 125: Generate STEP 5 Blocks.  OB 126: Define, Transfer Process Images  OB 129: Battery State  OB 131: Delete ACCUs 1, 2, 3 and 4.  OB 132/133: Roll-Up ACCU/Roll-Down ACCU  OB 141: "Disable Single Cyclic Timed Interrupts" On/Off  OB 142: "Delay All Interrupts" On/Off  OB 143: "Delay Single Cyclic Timed Interrupts" On/Off  OB 150: Set/Read System Time  OB 151: Set/Read Time for Clock-Controlled Interrupt  OB 153: Set/Read Time for Delayed Interrupt  OB 180: Variable Data Block Access                                   | 6 - 17<br>6 - 20<br>6 - 25<br>6 - 26<br>6 - 27<br>6 - 35<br>6 - 35<br>6 - 43<br>6 - 50<br>6 - 53<br>6 - 57 |

| 6.20   | OB 222: Restart Cycle Monitoring Time                                          |

|--------|--------------------------------------------------------------------------------|

| 6.21   | OB 223: Compare Start-Up Modes                                                 |

| 6.22   | OB 254/255: Copy/Duplicate Data Blocks                                         |

| 7      | Extended Data Block DX 07 -                                                    |

| 7.1    | Application                                                                    |

| 7.2    | Structure of DX 0                                                              |

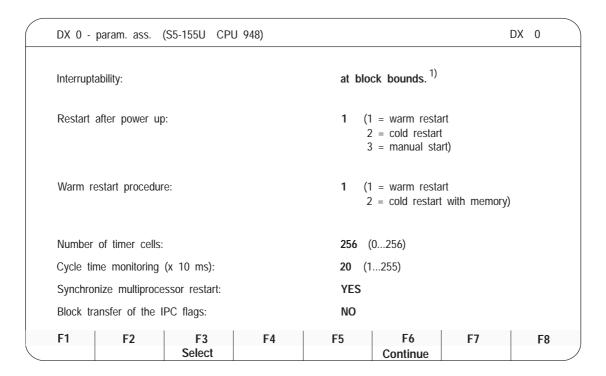

| 7.2.1  | Example of Input in DX 07 -                                                    |

| 7.3    | Parameters for DX 0                                                            |

| 7.4    | Examples of Parameter Assignment                                               |

| 7.4.1  | STEP 5 Programming                                                             |

| 7.4.2  | Parameter Assignment using the PG Screen Form                                  |

| 8      | Memory Assignment and Memory Organization 8 -                                  |

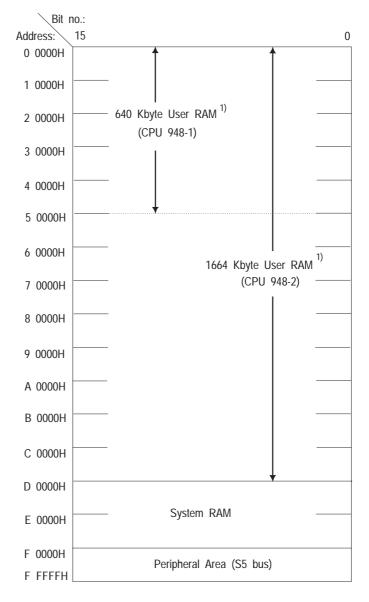

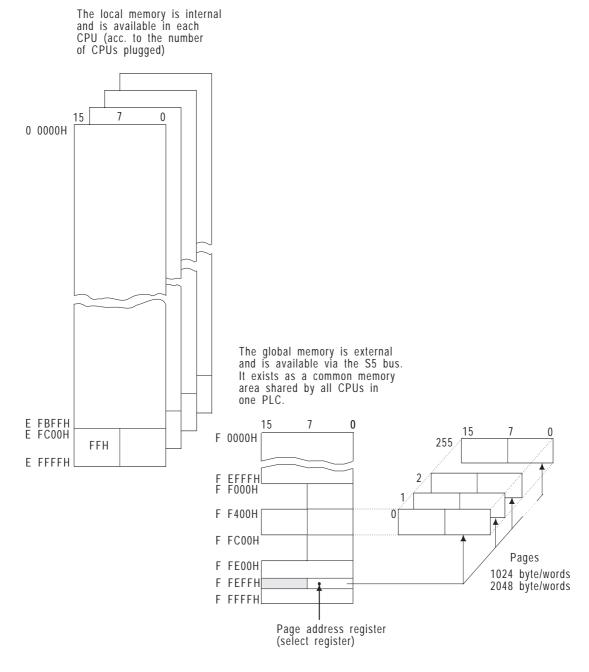

| 8.1    | Structure of the Memory Area                                                   |

| 8.2    | Memory Assignment in the CPU 948 8 -                                           |

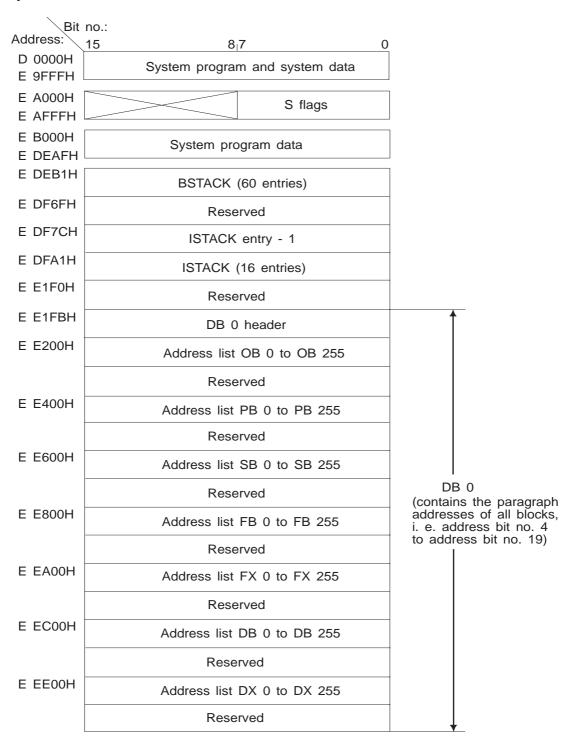

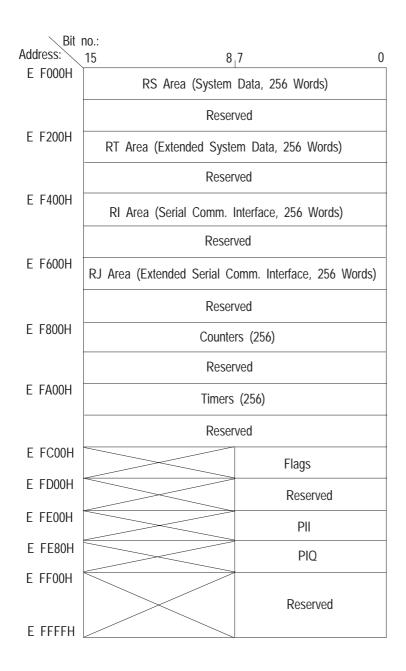

| 8.2.1  | Memory Assignment for the System RAM 8 -                                       |

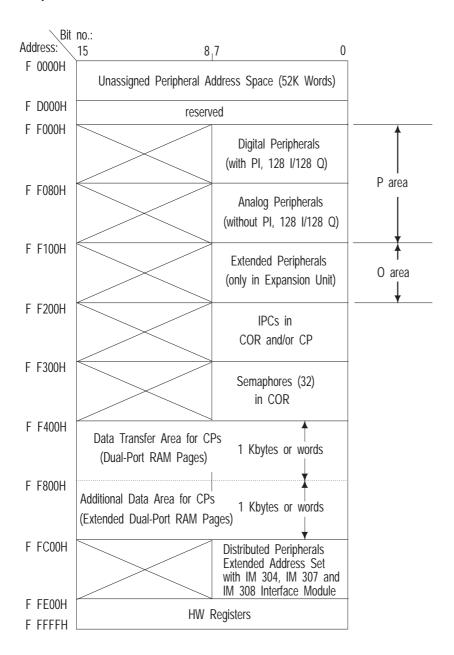

| 8.2.2  | Memory Assignment for the Peripherals                                          |

| 8.3    | User Memory Organization in the CPU 948 8 - 1                                  |

| 8.3.1  | Block Headers in User Memory                                                   |

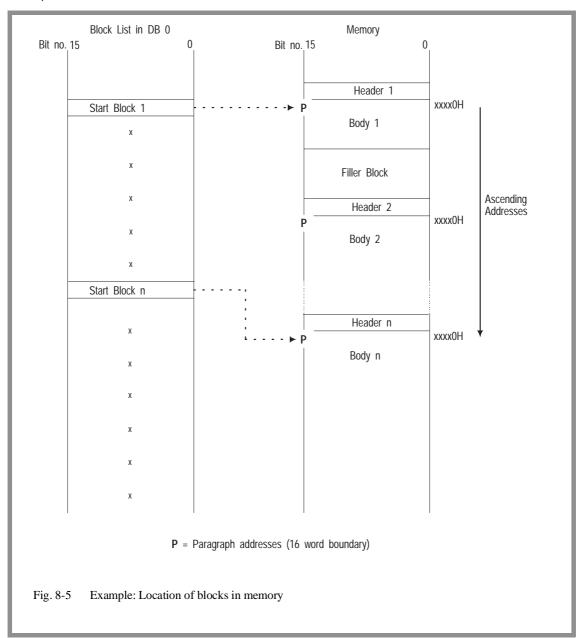

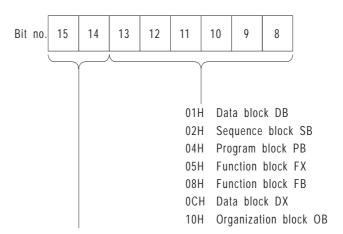

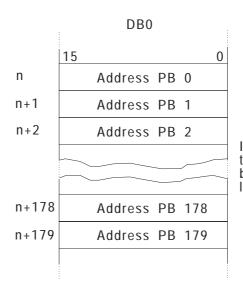

| 8.3.2  | Block Address List in Data Block DB 0                                          |

| 8.3.3  | RI/RJ Area                                                                     |

| 8.3.4  | RS/RT Area                                                                     |

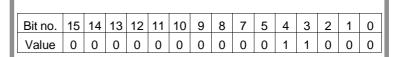

| 8.3.5  | Bit Assignment of the System Data Words                                        |

| 8.3.6  | Addressable System Data Area                                                   |

| 9      | Memory Access Using Absolute Addresses 9 -                                     |

| 9.1    | Introduction                                                                   |

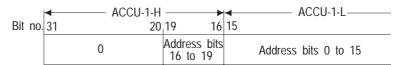

| 9.2    | Memory Access via Address in ACCU 1                                            |

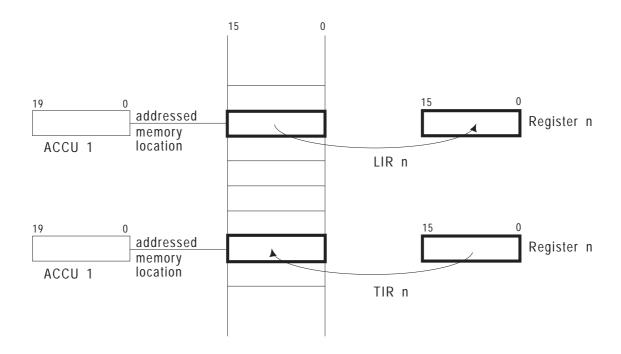

| 9.2.1  | LIR/TIR: Loading to or Transferring from a 16-Bit Memory Area Indirectly 9 -   |

| 9.2.2  | Examples of Access to DW $>$ 255                                               |

| 9.2.3  | LDI/TDI: Loading to or Transferring from a 32-Bit Memory Area Indirectly 9 - 1 |

| 9.3    | Transferring Memory Blocks                                                     |

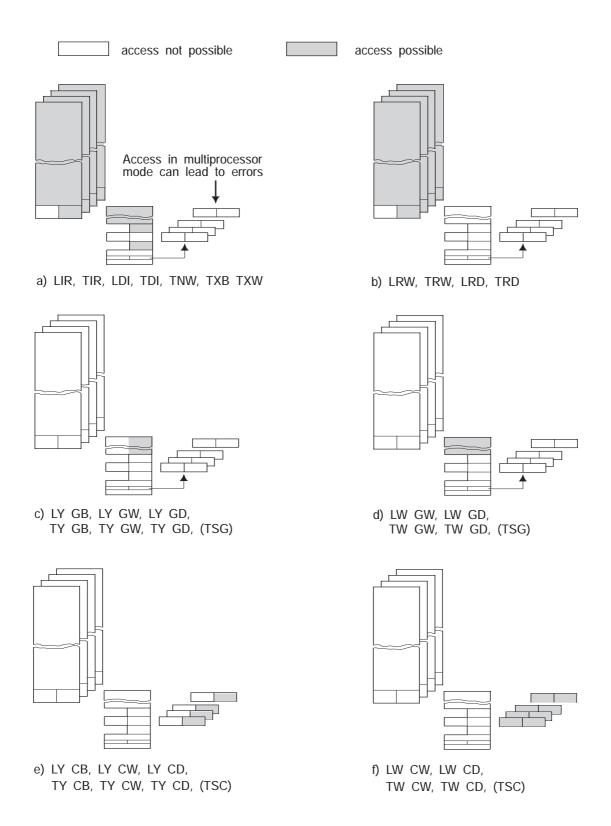

| 9.4    | Operations with the Base Address Register (BR Register)                        |

| 9.4.1  | Operations for Transfer between Registers                                      |

| 9.4.2  | Accessing the Local Memory                                                     |

| 9.4.3  | Accessing the Global Memory                                                    |

| 9.4.4  | Accessing the Dual-Port RAM Memory                                             |

| 10     | Multiprocessor Mode and Communication in the S5-155U 10 -                      |

| 10.1   | Multiprocessor Mode                                                            |

| 10.1.1 | When to use the Multiprocessor Mode                                            |

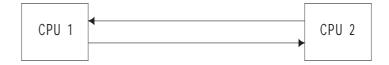

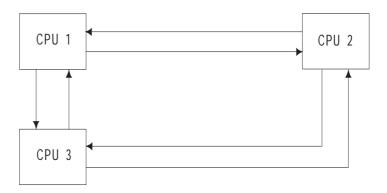

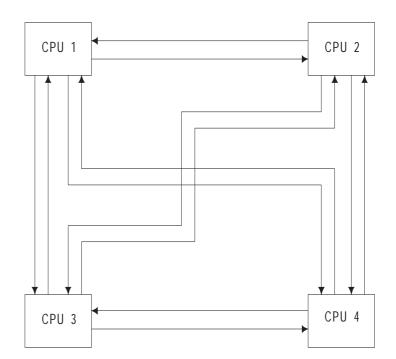

| 10.1.2 | What Communications Mechanisms are Available? 10 -                             |

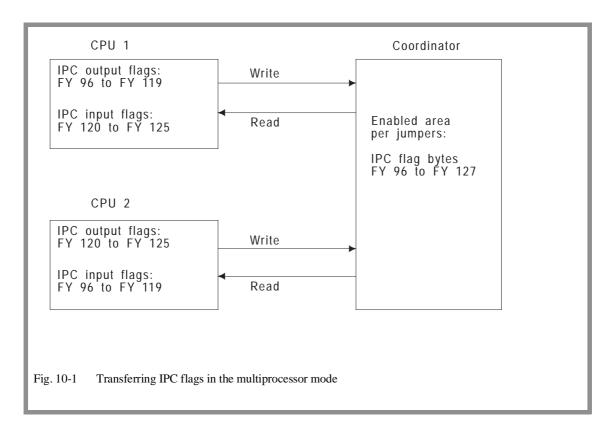

| 10.1.3 | Exchanging Data via IPC Flags.                           | . 10 - 5 |

|--------|----------------------------------------------------------|----------|

| 10.1.4 | Exchanging Data via Handling Blocks                      | . 10 - 8 |

| 10.1.5 | What needs to be Programmed for the Multiprocessor Mode? | . 10 - 9 |

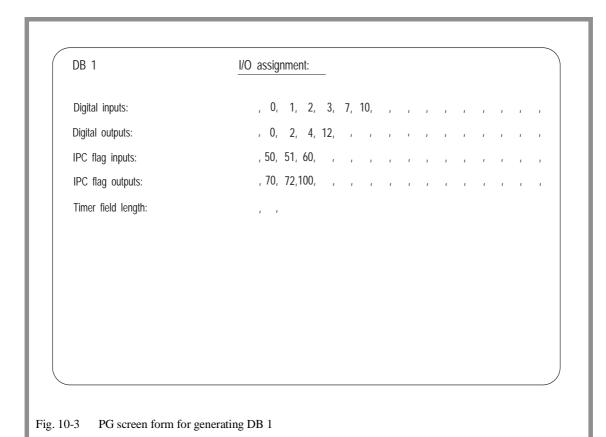

| 10.1.6 | How to Create Data Block DB 1                            | . 10 - 9 |

| 10.1.7 | Starting up in the Multiprocessor Mode                   | 10 - 13  |

| 10.1.8 | Test Mode                                                | 10 - 14  |

| 10.2   | Multiprocessor Communication                             | 10 - 15  |

| 10.2.1 | Introduction                                             | 10 - 15  |

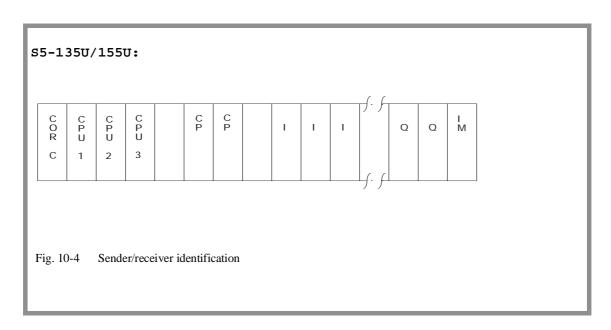

| 10.2.2 | How the Transmitter and Receiver are Identified          | 10 - 16  |

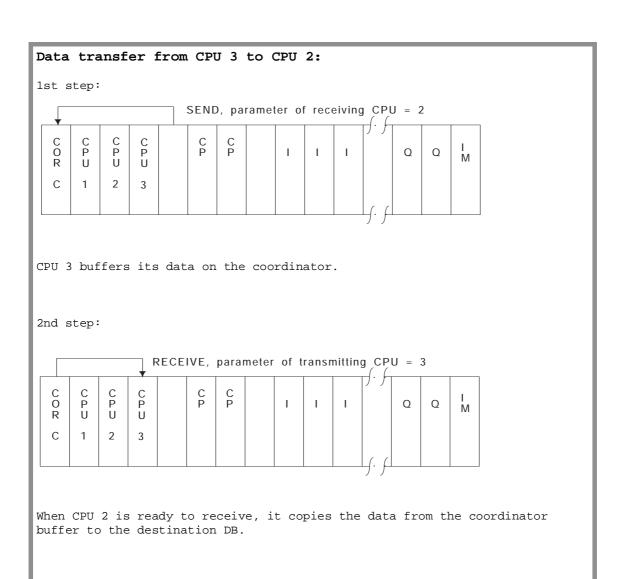

| 10.2.3 | Why Data is Buffered                                     | 10 - 17  |

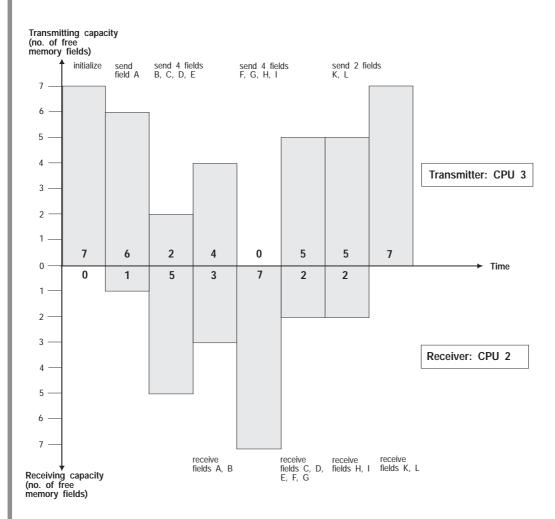

| 10.2.4 | How the Buffer is Processed and Managed                  | 10 - 18  |

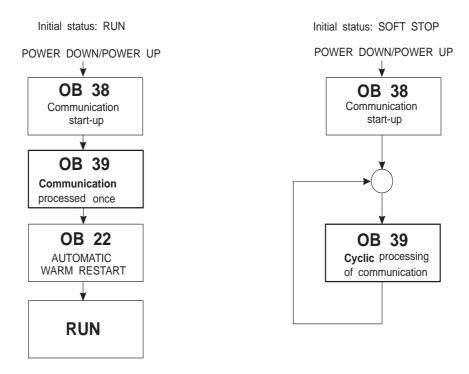

| 10.2.5 | System Start-Up                                          | 10 - 21  |

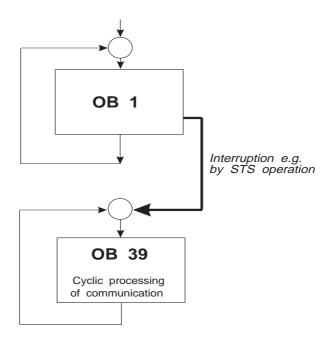

| 10.2.6 | Calling Communication OBs                                | 10 - 22  |

| 10.2.7 | How to Assign Parameters to Communication OBs            | 10 - 23  |

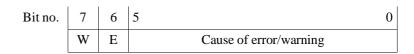

| 10.2.8 | How to Evaluate the Output Parameters                    | 10 - 24  |

| 10.3   | Runtimes of the Communication OBs                        | 10 - 31  |

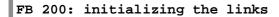

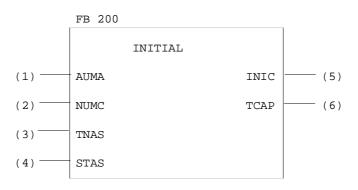

| 10.4   | INITIALIZE Function (OB 200)                             | 10 - 33  |

| 10.4.1 | Function                                                 | 10 - 33  |

| 10.4.2 | Call Parameters                                          | 10 - 35  |

| 10.4.3 | Input Parameters                                         | 10 - 35  |

| 10.4.4 | Output Parameters                                        | 10 - 38  |

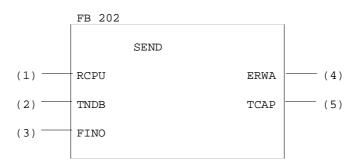

| 10.5   | SEND Function (OB 202)                                   | 10 - 40  |

| 10.5.1 | Function                                                 | 10 - 40  |

| 10.5.2 | Call Parameters                                          | 10 - 40  |

| 10.5.3 | Input Parameters                                         | 10 - 40  |

| 10.5.4 | Output Parameters                                        | 10 - 42  |

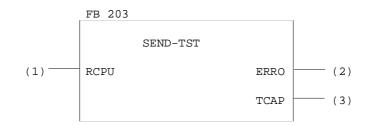

| 10.6   | SEND TEST Function (OB 203)                              | 10 - 45  |

| 10.6.1 | Function                                                 | 10 - 45  |

| 10.6.2 | Call Parameters                                          | 10 - 45  |

| 10.6.3 | Input Parameters                                         | 10 - 45  |

| 10.6.4 | Output Parameters                                        | 10 - 45  |

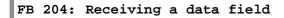

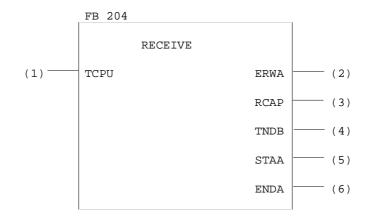

| 10.7   | RECEIVE Function (OB 204)                                | 10 - 47  |

| 10.7.1 | Function                                                 | 10 - 47  |

| 10.7.2 | Call Parameters                                          | 10 - 47  |

| 10.7.3 | Input Parameters                                         | 10 - 47  |

| 10.7.4 | Output Parameters                                        | 10 - 48  |

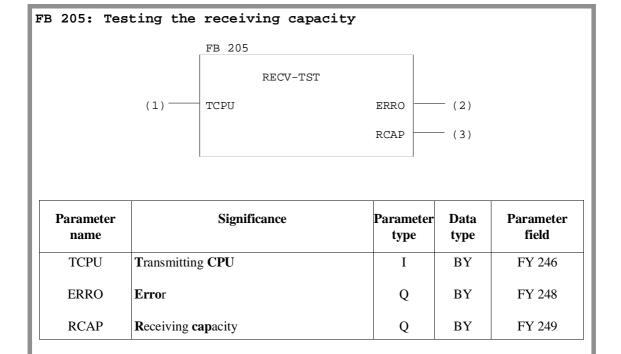

| 10.8   | RECEIVE TEST Function (OB 205)                           | 10 - 51  |

| 10.8.1 | Function                                                 | 10 - 51  |

| 10.8.2 | Call Parameters.                                         | 10 - 51  |

| 10.8.3 | Input Parameters                                         | 10 - 51  |

| 10.8.4 | Output Parameters                                        | 10 - 51  |

### Contents

| 10.9   | Applications                                          | 10 - 53 |

|--------|-------------------------------------------------------|---------|

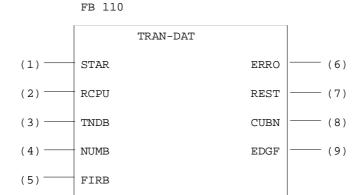

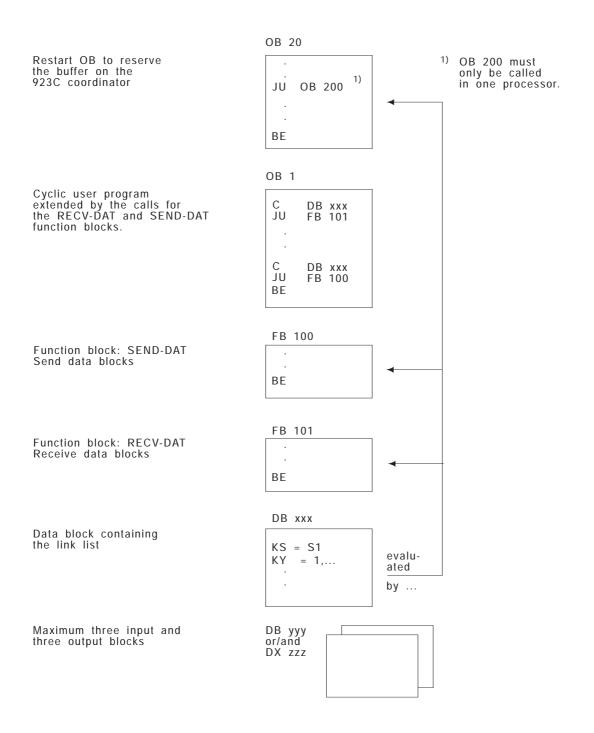

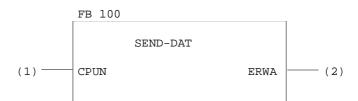

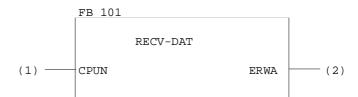

| 10.9.1 | Calling the Special Function OB using Function Blocks | 10 - 53 |

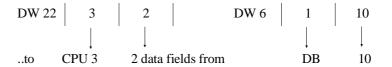

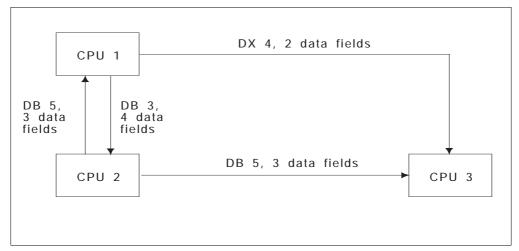

| 10.9.2 | Transferring Data Blocks                              | 10 - 60 |

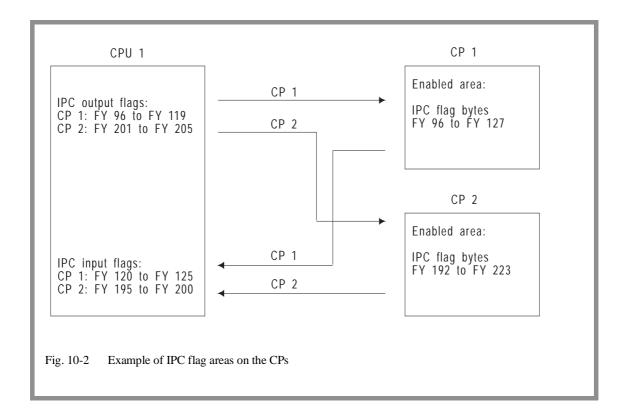

| 10.9.3 | Extending the IPC Flag Area                           | 10 - 66 |

| 11     | PG Interfaces and Functions                           | 11 - 3  |

| 11.1   | Overview                                              | 11 - 4  |

| 11.2   | PG Functions                                          | 11 - 5  |

| 11.2.1 | Info 11 - 6                                           |         |

| 11.2.2 | Installation                                          | 11 - 7  |

| 11.2.3 | Program Test                                          | 11 - 8  |

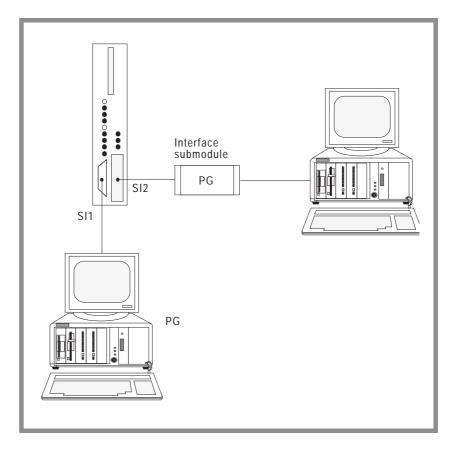

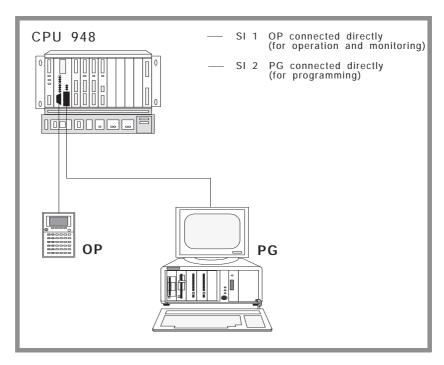

| 11.3   | Serial Link PG - PLC via 1st or 2nd Serial Interface  | 11 - 16 |

| 11.4   | Parallel Operation of Two Serial PG Interfaces        | 11 - 17 |

| 11.4.1 | Installation                                          | 11 - 19 |

| 11.4.2 | Operation                                             | 11 - 19 |

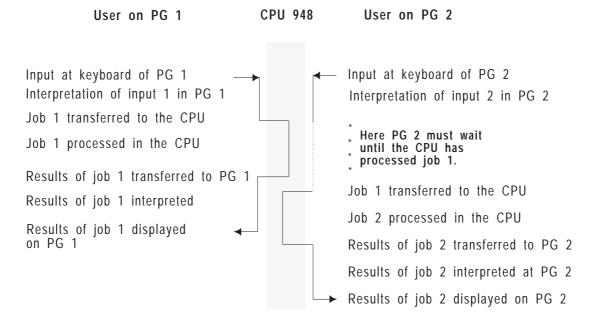

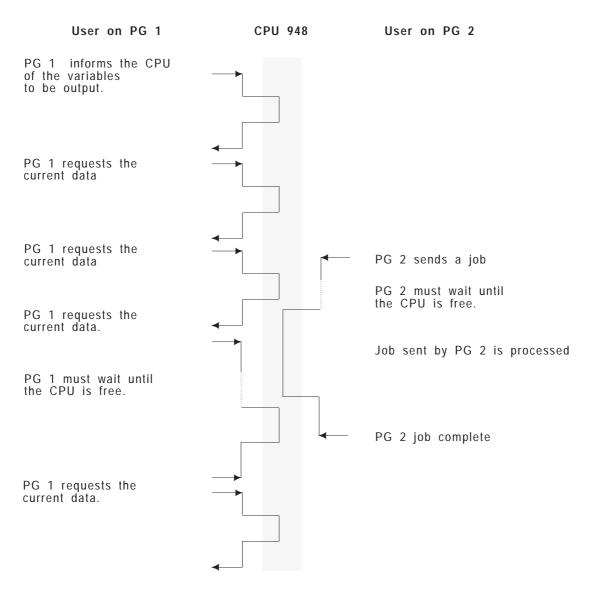

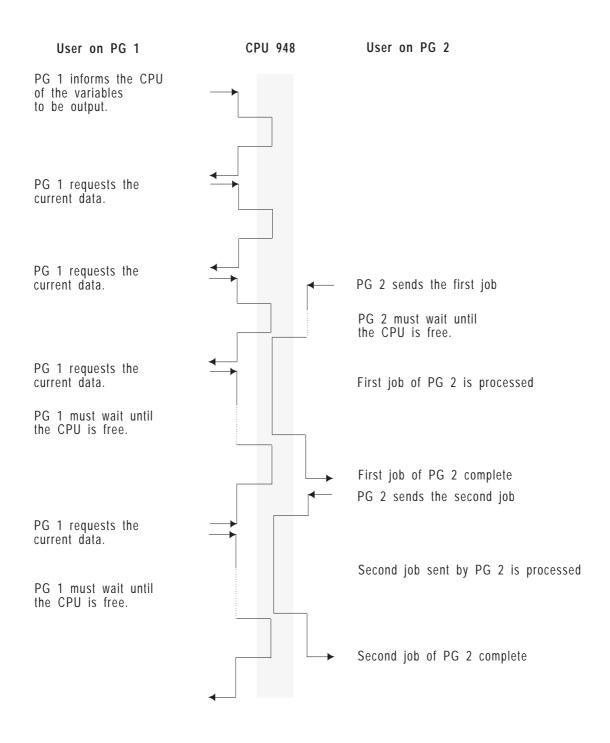

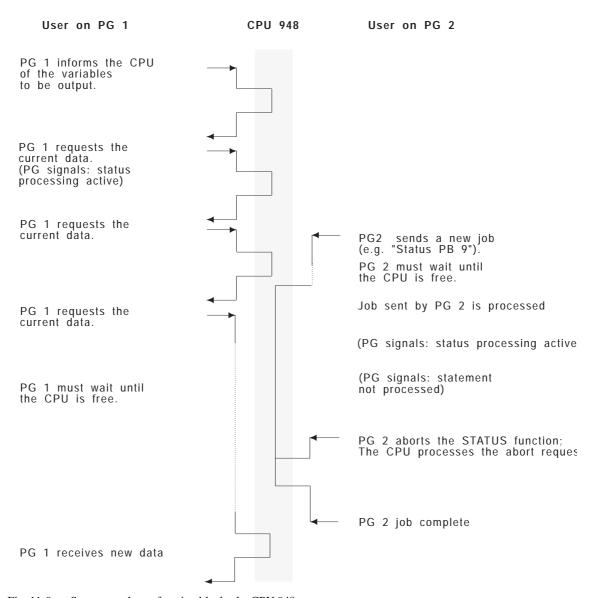

| 11.4.3 | Sequence in Certain Operating Situations              | 11 - 21 |

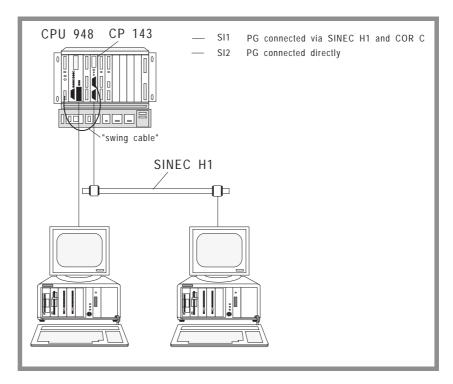

| 11.5   | PG Functions via the S5 Bus                           | 11 - 27 |

| 11.5.1 | Application                                           | 11 - 27 |

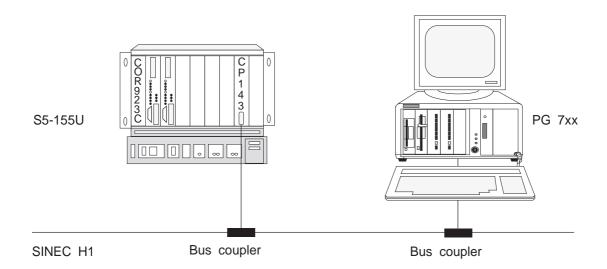

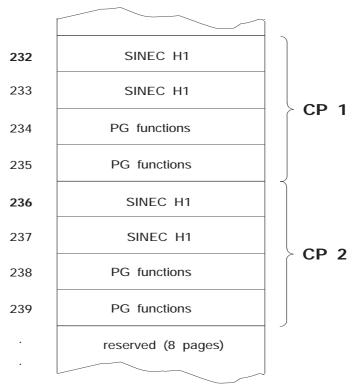

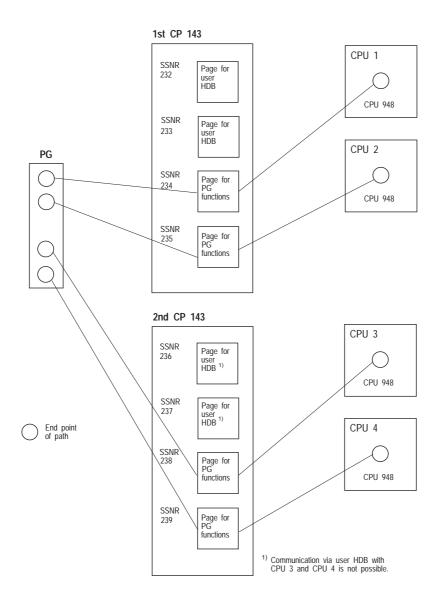

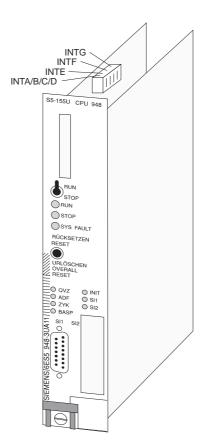

| 11.5.2 | How the PG Functions Work via the S5 Bus              | 11 - 29 |

| 11.5.3 | Installation and Getting Started                      | 11 - 31 |

| 11.5.4 | Condition Codes Indicating Problems                   | 11 - 35 |

| 12     | Appendix                                              | 12 - 3  |

| 13     | Indexes                                               | 13 - 3  |

Introduction

# **Contents of Chapter 1**

| 1.1 | Area of Application for the S5-155U with the CPU 948     |

|-----|----------------------------------------------------------|

| 1.2 | Typical Mode of Operation of a CPU                       |

| 1.3 | The Programs in a CPU                                    |

| 1.4 | Which Operands are available to the User Program?        |

| 1.5 | How much Memory is available for the User Program?       |

| 1.6 | How to Tackle Programming?                               |

| 1.7 | Programming Tools. 1 - 18                                |

| 1.8 | Converting User Programs of the CPU 928B for the CPU 948 |

Introduction

Aims of the manual

This manual is intended to provide specialized information about programming the CPU 948 for users who already have basic knowledge of programming PLCs and want to use the CPU 948 in the S5-155U programmable controller. If you do not yet have this basic knowledge, we strongly advise you read the documentation introducing the programming language STEP 5 /3/ or take part in a course at our training center. SIEMENS provides comprehensive training for SIMATIC S5. For more detailed information, contact your local SIEMENS office.

Contents of Chapter 1

Chapter 1 explains how to use the manual and deals with the areas of application of the S5-155U programmable controller with the CPU 948 and its structure.

The chapter explains the typical mode of operation of a CPU and the structure of the CPU program.

You will also find a few suggestions about how to tackle programming and will learn some of the features of the CPU 948 which are important for programming.

If you have already worked with the CPU 946/947 and would like to know the differences between these modules and the CPU 948, refer to Section 1.8.

Chapter 1 also informs you about differences between versions A01 and A02 of the CPU 948 and explains points you should remember when converting "928B" programs for the CPU 948.

# 1.1 Area of Application for the S5-155U with the CPU 948

SIMATIC S5 family

The S5-155U programmable controller belongs to the family of SIMATIC S5 programmable controllers. With the CPU 948, it is the most powerful multiprocessor unit for process automation (open and closed loop control, signalling, monitoring, logging). Owing to its modularity and high performance, it can be used for medium to extremely large control systems as well as for complex automation tasks at the plant and process supervision level.

Suitability

The S5-155U with the CPU 948 is particularly suitable for the following:

- Tasks requiring fast bit and word-oriented processing and fast reaction times, i.e. with extremely fast open and closed loop controls. Examples of this are fast processes in mechanical engineering (bottling plant, packing machines or similar systems) and in the automobile industry.

- Tasks requiring an extremely high storage capacity and fast access times, e.g. in the automobile industry, process and plant engineering.

- Tasks requiring fast communication with other CPUs installed in the PLC and operating in the multiprocessor mode and with CP modules (e.g. when connected to bus systems, host computers, for visualization, operation and monitoring).

- Complex tasks which can be handled efficiently and clearly using the high level languages C and SCL.

# 1.2 Typical Mode of Operation of a CPU

*Mode of operation of a CPU* The following modes of operation are possible in a CPU:

Cyclic processing

This is the main part of all activities in the CPU. As the name already says, the same operations are repeated in an endless cycle.

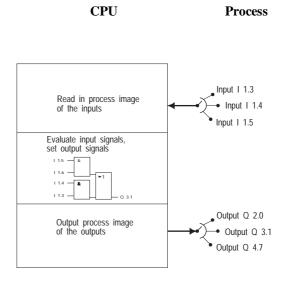

Cyclic processing can be divided into three main phases, as follows:

| Phase | Sequence                                                                                                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | All the input modules assigned to the CPU are scanned by the system program and the values read in are stored in the process image of the inputs (PII). |

| 2     | The values contained in the PII are processed by the user program and the values to be output are entered in the process image of the outputs (PIQ).    |

| 3     | The values contained in the process image of the outputs are output by the system program to the output modules assigned to the CPU.                    |

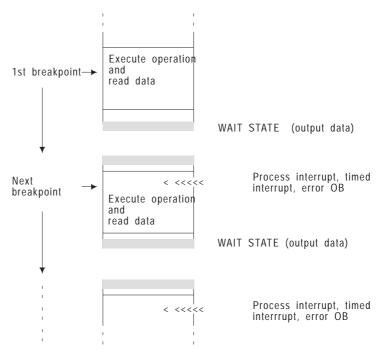

#### Time-controlled processing

In addition to the cyclic processing, **time-controlled** processing is also available for processes requiring control signals at constant intervals, e.g. non-time critical monitoring functions performed every second.

#### Interrupt-driven processing

If the reaction to a particular process signal must be particularly fast, this should be handled with **interrupt-driven** processing. With, for example, a system interrupt, triggered via an interrupt generating module, you can activate a special processing section within your program.

# Processing according to priority

The types of processing listed above are handled by the CPU according to their **priority**.

Since a fast reaction is required to a time or interrupt event, the CPU interrupts cyclic processing to handle a time or interrupt event. Cyclic processing therefore has the lowest priority.

Whether or not the time-controlled processing is more important than the interrupt controlled processing depends, among other things, on the particular task. For this reason, the priority of time and interrupt-driven processing on the CPU 948 can be selected.

# 1.3 The Programs in a CPU

The program existing on every CPU is divided into the following:

the system program

and

the user program.

#### System program

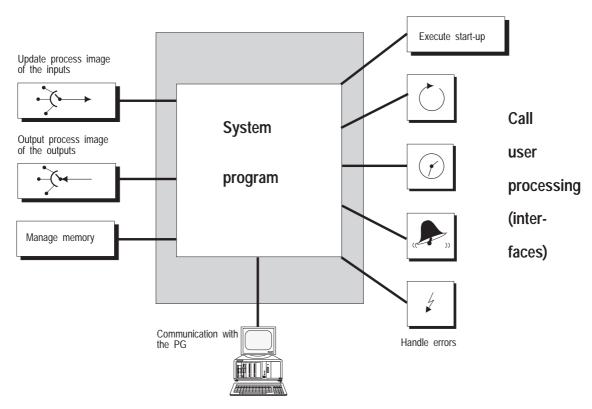

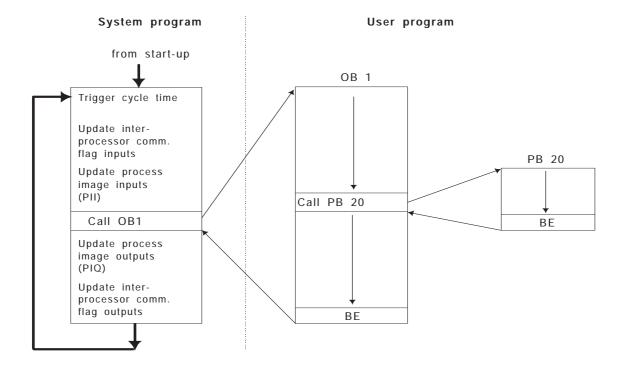

The system program organizes all the functions and sequences of the CPU which do not involve a specific control task (refer to Fig. 1-2).

Fig. 1-1 Tasks of the system program

Tasks

The tasks include the following: 1)

- cold and warm restart,

- updating the process image of the inputs and outputting the process image of the outputs,

- calling the cyclic, time-controlled and interrupt-driven programs,

- · detection and handling of errors,

- memory management,

- communication with the programmer (PG).

User interfaces

As the user, you can influence the reaction of the CPU to particular situations and errors via special interfaces to the system program.

Storing the system program

After switching on the power supply to the PLC (POWER UP) the system program is read from the EPROM to the internal operating system RAM.

System program defaults

The following chapters, except for Chapter 7, describe the **default system reaction** to process events or errors. Depending on the defaults, the CPU changes to the stop mode if an operation code error occurs and the error organization block is not loaded.

Modifying the defaults

You can modify the system response by assigning parameters for the data block DX 0.

${\bf Chapter~7~describes~the~system~response~{\bf following~modification}}.$

<sup>1)</sup> When operating with several CPUs (multiprocessing) further tasks are involved.

### User program

Tasks

The user program contains all the functions required for processing a **specific control task**. In general terms, these functions can be assigned to the interface provided by the system program for the various types of processing, as follows:

| Type of processing          | Task                                                                                                                                                                                                                 |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cold and warm restart       | To provide the conditions under which<br>the other processing functions can start<br>from a defined status following a cold or<br>warm restart of the control system (e.g.<br>assigning specific values to signals). |

| Cyclic processing           | Constantly repeated signal processing (e.g. logic operations on binary signals, reading in and analyzing analog values, specifying binary signals for output, outputting analog values).                             |

| Time-controlled processing  | Special, time-dependent processing with the following time conditions: - faster than the average cycle, - at a time interval greater than the average cycle time, - at a specified point in time.                    |

| Interrupt-driven processing | Special, fast reactions to certain process signals.                                                                                                                                                                  |

| Error reaction              | Handling problems within the normal sequence of the program.                                                                                                                                                         |

#### Structure

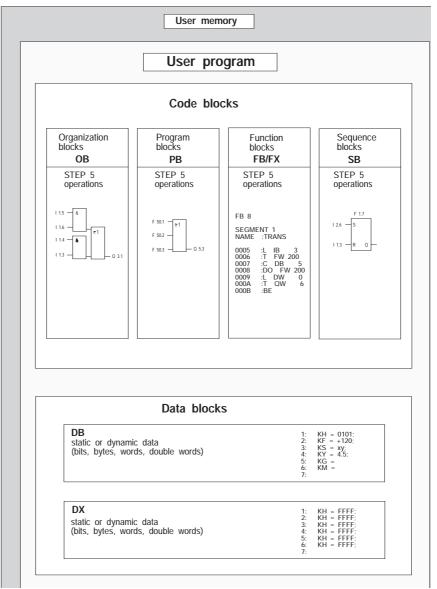

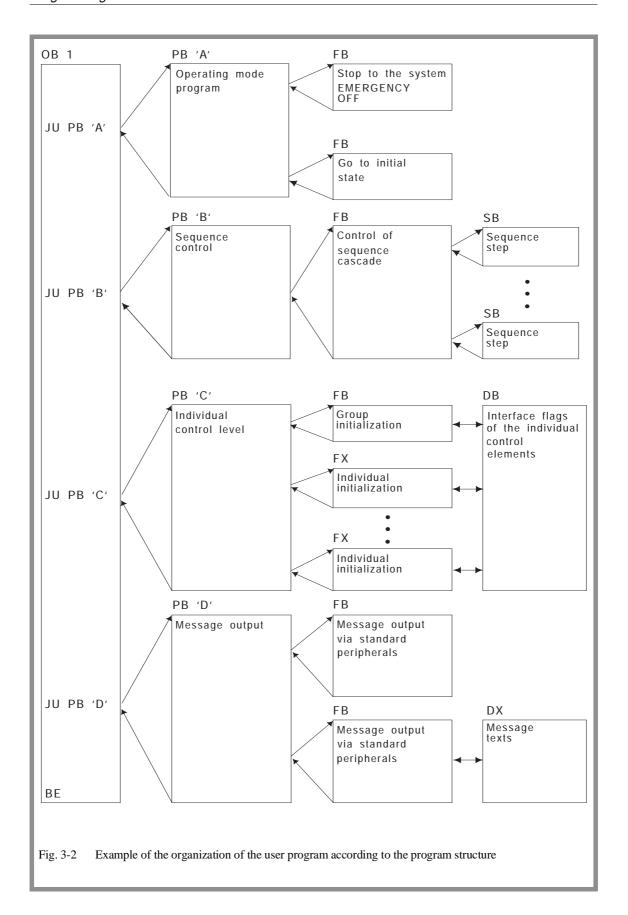

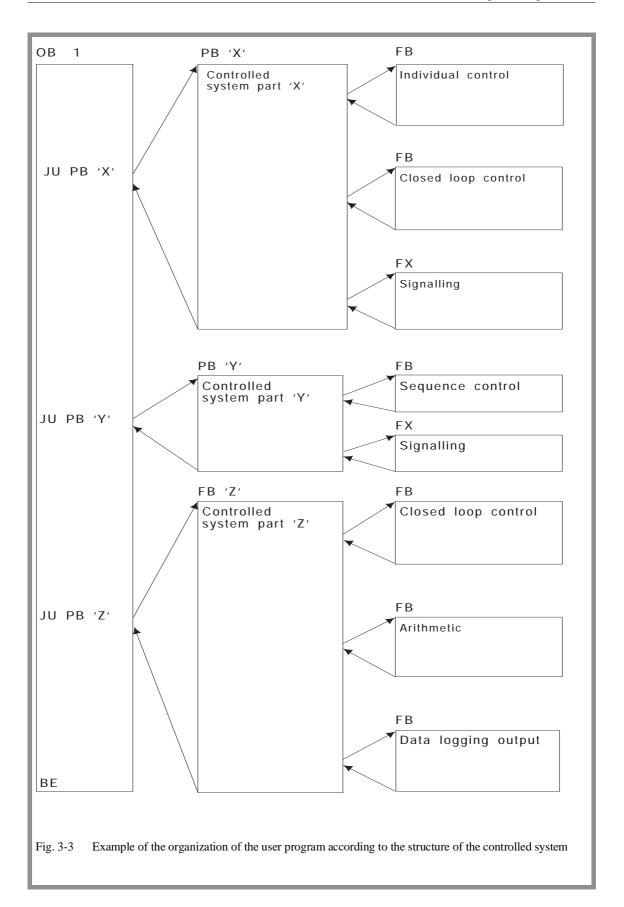

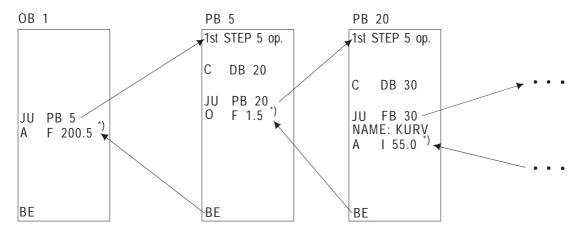

Fig. 1-2 Structure of a STEP 5 user program

#### Storing the user program

After programming the user program, you must load it in the user memory of the CPU 948 (directly from the PG) or via a memory card whose contents are copied to the user memory by an OVERALL RESET of the CPU.

# Interfaces to the system program

**Organization** blocks are available as interfaces to the system program for the special types of processing.

# 1.4 Which Operands are available to the User Program?

The CPU 948 provides the following operand areas for programming:

- process image and I/Os

- flags (F flags and S flags)

- timers/counters

- data blocks

# Process image of the inputs and outputs PII/PIQ

| Characteristics                                                                                                                              | Size                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| The user program can access the following data types in the process image extremely quickly: - single bits, - bytes, - words, - double words | 128 bytes<br>each for<br>inputs and<br>outputs |

### I/O area (P area)

| Characteristics                                                      | Size                          |

|----------------------------------------------------------------------|-------------------------------|

| The user program can access the I/O modules directly via the S5 bus. | 256 bytes each for inputs and |

| The following data types are possible: - bytes, - words.             | outputs                       |

### Extended I/O area (O area)

| Characteristics                                                      | Size                                |

|----------------------------------------------------------------------|-------------------------------------|

| The user program can access the I/O modules directly via the S5 bus. | 256 bytes<br>each for<br>inputs and |

| The following data types are possible: - bytes, - words.             | outputs                             |

# F flags

| Characteristics                                                                                                                                                                                                                                                                          | Size      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| The flag area is a memory area which the user program can access extremely quickly with certain operations.  The flag area should be used ideally for working data required often.                                                                                                       | 2048 bits |

| The following data types can be accessed: - single bits, - bytes, - words, - double words.                                                                                                                                                                                               |           |

| Single flag bytes can be used as <b>interprocessor communication flags</b> (IPC flags) to exchange data between the CPUs in the multiprocessor mode (refer to Chapter 10). IPC flags are updated by the system program at the end of the cycle via a buffer in the coordinator or CP/IP. |           |

# S flags (extended flag area)

| Characteristics                                                                                                                                                                                                                     | Size        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| The CPU 948 also contains an additional flag area, the S flag area. The user program can also access this area extremely quickly as with the F flags.                                                                               | 32 768 bits |

| S flags <b>cannot</b> however by used as <b>actual operands</b> with function block calls nor as <b>IPC flags</b> for data exchange between the CPUs. The bit test operations of the CPU 948 can also not be used with the S flags. |             |

| These flags can only be used with the PG system software "S5-DOS" from version 3.0 upwards or "S5-DOS/MT" from version 1.0 upwards.                                                                                                 |             |

# Timers (T)

| Characteristics                                                                                                                                                                                                     | Size               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| The user program loads timer cells with a time value between 10 ms and 9990 s and by means of a start operation, decrements the timer from this value at the preselected intervals until it reaches the value zero. | 256 timer<br>cells |

## Counters (C)

| Characteristics                                                                                            | Size         |

|------------------------------------------------------------------------------------------------------------|--------------|

| The user program loads counter cells with a start value (max. 999) and then increments or decrements them. | 256 counters |

# Data words in the current data block

| Characteristics                                         | Size  |

|---------------------------------------------------------|-------|

| A data block contains constants and/or variables in the | 256   |

| byte, word or double word format. With STEP 5           | words |

| operations, you can always access the "current" data    |       |

| block (refer to Section 2.4.2).                         | 1)    |

| The following data types can be accessed:               |       |

| - single bits,                                          |       |

| - bytes,                                                |       |

| - words,                                                |       |

| - double words.                                         |       |

In data blocks with a length greater than 256 words, you can only access data words with the numbers > 255 with operations for absolute memory access (refer to Chapter 9).

# 1.5 How much Memory is available for the User Program?

For storing logic and data blocks, the CPU 948 only has the user memory in the internal RAM.

The CPU 948 is available with two versions of the user memory:

- Version 1: with 640 Kbytes,

- Version 2: with 1,664 Kbytes.

## 1.6 How to Tackle Programming

If you are an experienced user, you have probably found the most suitable method for creating programs for yourself and you can skip this section.

Less experienced readers will find tips for designing, programming, testing and starting up your STEP 5 program.

#### Implementation stages

The implementation of the STEP 5 control program can be divided into three stages:

| Stage | Activity                                   |

|-------|--------------------------------------------|

| 1     | Determining the technological task         |

| 2     | Designing the program                      |

| 3     | Creating, testing and starting the program |

#### Recursive procedure

In practice, you will recognize that certain steps must be repeated (recursive procedure), e.g. when you realize that more signals are required to improve the handling of the task.

#### Stage 1

Determining the technological task:

| Stage | Activity                                                                                                                                |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Create a general block diagram outlining the control tasks of your process.                                                             |

| 2     | Create a list of the input and output signals required for the task.                                                                    |

| 3     | Improve the block diagram by assigning the signals and any particular time conditions and/or counter statuses to the individual blocks. |

### Stage 2

#### Designing the program

| Stage | Activity                                                                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Based on the improved block diagram, decide on the types of processing required of your program (cyclic processing, time-controlled processing etc.) and select the OBs required for this. |

| 2     | Divide the types of processing into technological and/or functional units.                                                                                                                 |

| 3     | Check whether the units can be assigned to a program or function block and select the blocks you require (PB x, FB y etc.)                                                                 |

| 4     | Find out which timers, counters and data or results memory you require.                                                                                                                    |

| 5     | Specify the tasks for each of the proposed logic blocks and the data for flags and data blocks which may be required. Create flow diagrams for the logic blocks.                           |

# Notes on the scope of cyclic processing

When deciding on the types of processing, keep the following conditions in mind:

- The cycle must run through quickly enough. The process statuses must not change more quickly than the CPU can react. Otherwise the process can get out of control.

- The maximum reaction time should be taken as twice the cycle time.

The cycle time is determined by the cyclic processing of the system program and the type and scope of the user program. It is often not constant, since the cyclic user program may be interrupted when time and interrupt-driven program sections are called.

### Stage 3

Creating, testing and starting up the program:

| Stage | Activity                                                                                                                                                                                |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Decide on the type of representation for the logic blocks (LAD, CSF or STL, refer to Chapter 2). Remember that function blocks can only be created in the STL method of representation. |

| 2     | Program all logic and data blocks (please refer to your STEP 5 manual).                                                                                                                 |

| 3     | Start up the blocks one after the other (you may have to program a different OB for each individual step, to call the logic blocks):  1a: load the block(s)  1b: test the block(s)      |

|       | (For more detailed information please refer to your STEP 5 manual and Chapter 11).                                                                                                      |

| 4     | When you are certain that all the logic blocks run correctly and all the data can be correctly calculated and stored, you can start up your whole program.                              |

#### Note on test strategies

When you actually start up your program for the first time in genuine process operation, i.e. with real input and more importantly output signals, is a decision that must be left up to yourself or to a team of experts.

The more complex the process, the greater the risk and therefore the greater the care required when starting up.

## 1.7 Programming Tools

#### Suitable PGs

The following programmers are available for creating your user program, PG 685, PG 710, PG 730, PG 750 and PG 770. You can check on the performance and characteristics of these devices in the catalog ST 59 /9/.

#### Note

If you wish to use the **full range of performance** of the CPU 948 in your automation software, (particularly the DX 0 screen, the "Output ISTACK" screen, the display with the "memory configuration" function and the PG functions via the backplane bus) you require the PG system software "STEP 5/ST" from version 6.3 upwards or "STEP 5/MT" from version 6.0 upwards plus the "Delta diskette CPU 948" and a PG 7xx.

#### Suitable software

You can create user programs for SIMATIC S5 programmable controllers as follows:

• In the **STEP 5** programming language,

Here you require the STEP 5 programming package along with the system software STEP 5/ST or STEP 5/MT (description, refer to /3/ in Further Reading),

or

• In a higher programming language:

If you are familiar with programming in higher programming languages, you can also formulate your STEP 5 program for the CPU 948 as follows:

SCL (refer to /12/ in Further Reading, the SCL compiler is contained in the PG software "S5-DOS/MT" from version 6 upwards.)

or

- C with S5 C compiler (refer to /13/ in Further Reading).

You can also create **programs for sequence control systems** in a graphic representation using the **GRAPH 5** programming package (description, refer to /4/ in Further Reading).

Depending on the task, you can also incorporate "off-the-peg" standard function blocks in your user program. The performance and characteristics of these blocks are described in the catalog ST 57 /11/.

# 1.8 Converting User Programs of the CPU 928B for the CPU 948

The following section informs you about the points you should remember when you convert user programs written for the CPU 928B for use on the CPU 948.

### Operations

In the following operations, note the differences in the execution and handling (among other things the different memory utilization).

| Operations                          | CPU 928B                                                                                                                                   | CPU 948                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IA/RA (disable/enable interrupts)   | All process interrupts are disabled or enabled                                                                                             | Only the process interrupts via input byte IB 0 are disabled or enabled. Instead of these operations, use the special function OBs OB 122 or OB 142.                                                                                                                                                                                                                                                                                       |

| LIR/TIR                             | 16 bit long addresses are used.                                                                                                            | 20 bit long addresses are used.<br>Adaptation is necessary.                                                                                                                                                                                                                                                                                                                                                                                |

| Block transfer operation TNB        | 16 bit long addresses are used.                                                                                                            | The operation does not exist. Use TNW for block transfer from the 8-bit to the 8-bit area.                                                                                                                                                                                                                                                                                                                                                 |

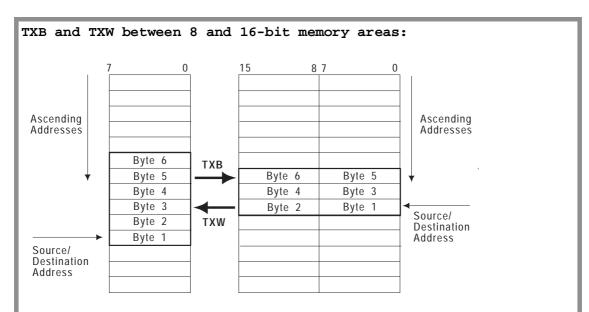

| Block transfer operation TNW        | <ul> <li>16 bit long addresses are used.</li> <li>Block transfers from the 8-bit to the 8-bit area and vice versa are possible.</li> </ul> | <ul> <li>20 bit long addresses are used. Adaptation is necessary.</li> <li>only block transfers from the 8-bit to the 8-bit area and from the 16-bit to the 16-bit areas possible with TNW.</li> <li>for the block transfer from the 8-bit to the 16-bit area use the operation TXB,</li> <li>for the block transfer from the 16-bit to the 8-bit area use the operation TXW.</li> <li>(TXB and TXW do not exist on a CPU 928B)</li> </ul> |

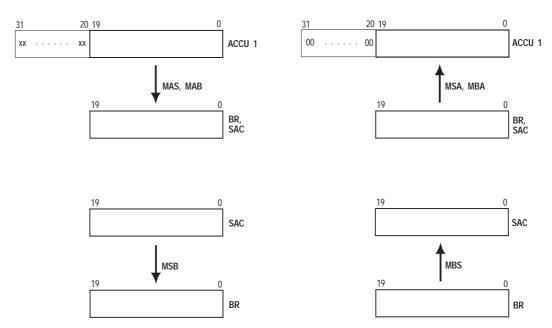

| All operations with the BR register | The BR register is 20 bits wide.                                                                                                           | The BR register is 32 bits wide.<br>Adaptation is necessary.                                                                                                                                                                                                                                                                                                                                                                               |

## Timer processing

| CPU 928B                                | CPU 948                                                                              |

|-----------------------------------------|--------------------------------------------------------------------------------------|

| The timers are updated during start-up. | The timers are only updated in the RUN mode (Reason: compatibility with CPU 946/947) |

# FB 0 as cycle block

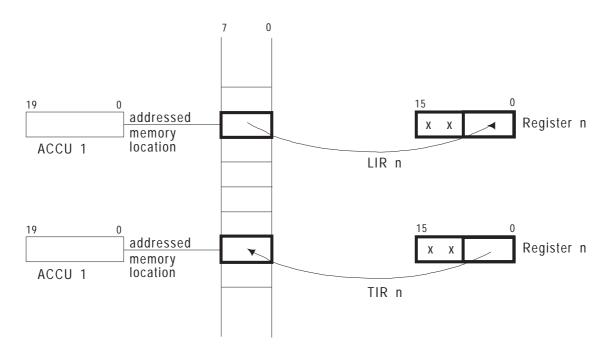

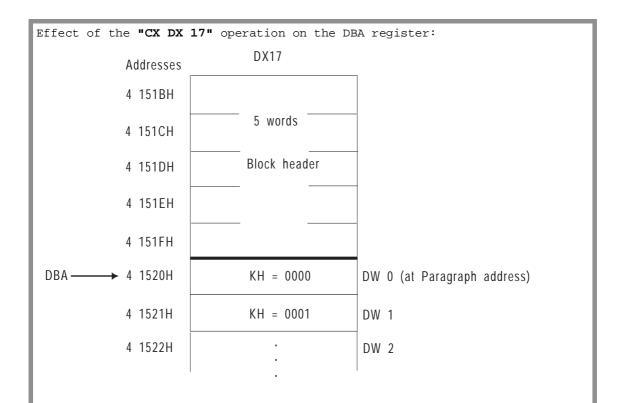

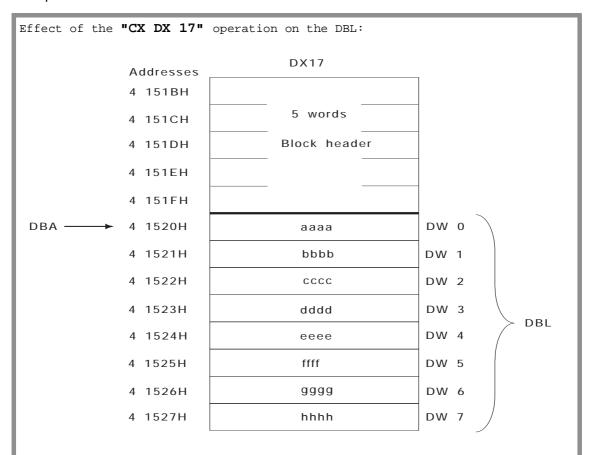

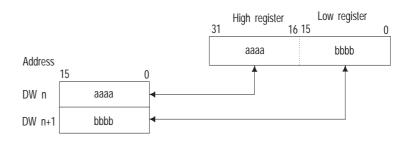

| CPU 928B                                                                                        | CPU 948                                                                                                           |