# ERTEC 200P

Enhanced Real-Time Ethernet Controller

# Manual

Edition (05/2013)

#### DISCLAIMER

WE HAVE CHECKED THE CONTENTS OF THIS MANUAL FOR AGREEMENT WITH THE HARDWARE AND SOFTWARE DESCRIBED. SINCE DEVIATIONS CANNOT BE PRECLUDED ENTIRELY, WE CANNOT GUARANTEE FULL AGREEMENT. HOWEVER, THE DATA IN THIS MANUAL ARE REVIEWED REGULARLY. NECESSARY CORRECTIONS ARE INCLUDED IN SUBSEQUENT EDITIONS. SUGGESTIONS FOR IMPROVEMENT ARE WELCOMED.

THIS MANUAL CONTAINS HYPERLINKS TO THE WEB SITES AS WELL AS TO ELECTRONIC DOCUMENTS OF THIRD PARTY COMPANIES. SIEMENS CANNOT BE HELD RESPONSIBLE FOR THE CONTENTS OF THESE WEB SITES AND ELECTRONIC DOCUMENTS, NOR DOES SIEMENS ADOPT THESE WEB SITES AND ELECTRONIC DOCUMENTS AND THEIR CONTENTS AS THEIR OWN. YOU THEREFORE USE THESE LINKS AT YOUR OWN RISK. SINCE SIEMENS IS NOT RESPONSIBLE FOR LINKED CONTENTS AND INFORMATION ON THE WEB SITES AND ELECTRONIC DOCUMENTS OF THIRD PARTIES, THIS INFORMATION IS NOT CHECKED BY SIEMENS.

COPYRIGHT

© SIEMENS AG 2013. ALL RIGHTS RESERVED

THE REPRODUCTION, TRANSMISSION OR USE OF THIS DOCUMENT OR ITS CONTENTS IS NOT PERMITTED WITHOUT EXPRESS WRITTEN AUTHORITY. OFFENDERS WILL BE LIABLE FOR DAMAGES. ALL RIGHTS, INCLUDING RIGHTS CREATED BY PATENT GRANT OR REGISTRATION OF A UTILITY MODEL OR DESIGN, ARE RESERVED.

ALL PRODUCT AND SYSTEM NAMES ARE REGISTERED TRADEMARKS OF THEIR RESPECTIVE OWNER AND MUST BE TREATED AS SUCH.

TECHNICAL DATA SUBJECT TO CHANGE.

# Preface

#### Target Audience of this Manual

This manual is intended for hardware developers who want to use the ERTEC 200P for new products. Experience working with processors and designing embedded systems and knowledge of Ethernet are required for this. It described all ERTEC function groups in details and provides information that you must take into account when configuring your own PROFINET IO device hardware.

The manual serves as a reference for software developers. The address areas and register contents are described in detail for all function groups.

Structure of this Manual

- Section 1 Overview of the ERTEC 200P.

- o Section 2 System features.

- Section 3 Hardware structure.

- Section 4 Hardware interfaces.

- o Section 5 Software interfaces.

- o Section 6 Miscellaneous

Scope of the Manual

This manual applies to the following product:

ERTEC 200P

This manual will be updated as required. You can find the current version of the manual on the Internet at <u>http://www.siemens.com/comdec</u>.

#### Guide

To help you quickly find the information you need, this manual contains the following aids:

- A complete table of contents as well as a list of all figures and tables in the manual are provided at the beginning of the manual.

- A glossary containing definitions of important terms used in the manual is located following the appendices.

- References to other documents are indicated by the document reference number enclosed in slashes (/No./). The complete title of the document can be obtained from the list of references at the end of the manual.

#### **Additional Support**

If you have questions regarding use of the described block that are not addressed in the documentation, please contact your Siemens representative.

Please send your written questions, comments, and suggestions regarding the manual to the hotline via the e-mail address indicated above.

In addition, you can receive general information, current product information, FAQs, and downloads pertaining to your application on the Internet at:

http://www.siemens.com/comdec.

#### **Technical Contacts for Germany / Worldwide**

| Siemens AG                         | Phone: +49 (0) 911/750-2080                             |

|------------------------------------|---------------------------------------------------------|

| Automation & Drives                | Fax: +49 (0) 911/750-2100<br>E-mail: ComDeC@siemens.com |

| ComDeC                             |                                                         |

| Street address:                    | Mailing address:                                        |

| Würzburgerstr.121                  | P.O. Box 2355                                           |

| 90766 Fürth<br>Federal Republic of | 90713 Fürth<br>Federal Republic of                      |

Germany

**Technical Contacts for USA**

Germany

PROFI Interface Center: One Internet Plaza PO Box 4991 Johnson City, TN 37602-4991

Fax: +1 (423)- 262- 2103 Phone: +1 (423)- 262- 2576 E-mail: pic.industry@siemens.com

# **Table of contents**

| 1 OVERVIEW OF THE ERTEC 200P                                                                | 9  |

|---------------------------------------------------------------------------------------------|----|

| 1.1 Switch functions                                                                        | 9  |

| 1.1.1 IRT communication                                                                     |    |

| 1.1.2 Performance upgrade at IRT communication                                              |    |

| 1.2 System functions                                                                        | 11 |

| 1.2.1 Use cases for the ERTEC 200P                                                          |    |

| 1.2.1.1 Use case 1 (UC1): Operation with external host                                      |    |

| 1.2.1.1 Use case 2 (UC2): Operation with external host                                      |    |

| 1.2.1.2 Ose case 2 (002). Operation without external nost                                   | 12 |

| 2 SYSTEM FEATURES                                                                           | 14 |

| <b>3</b> HARDWARE STRUCTURE                                                                 | 16 |

|                                                                                             | 10 |

| 3.1 Block diagram ERTEC 200P                                                                | 16 |

| 3.2 Overview of the ERTEC 200P IP utilization                                               |    |

| 3.3 Application notes                                                                       |    |

| 3.3.1 EMC SDRAM-Interface                                                                   |    |

| 3.3.2 EMC BurstFlash-Interface                                                              |    |

| 3.3.3 I-/D-TCM Mapping register of the ARM926 subsystems                                    |    |

| 3.3.4 I-TCM accesses of the ARM926 with 250MHz                                              |    |

| 3.3.5 Accesses to the IO-RAM in the Peripherie-Interface (Per-IF)                           |    |

| 3.3.6 Trigger of GDMA HW-Jobs by GPIOs 03 is not supported                                  |    |

| 3.3.7 Acknowledgement of the PN-ICU3 accumulative interrupts in the Event-Unit of the PerIF |    |

| 3.3.8 AHB Burstbreaker.                                                                     |    |

| 3.3.9 XSRST function at active XRESET                                                       |    |

| 3.3.10 EDC reporting                                                                        |    |

| 3.3.11 Cache-Parity-Check                                                                   |    |

| 3.3.12 Access Error                                                                         |    |

| 3.3.13 ARM926 Watchdog                                                                      |    |

| 3.3.14 PLL LOCK                                                                             |    |

| 3.3.15 PLL LOSS                                                                             |    |

| 3.3.16 Software Reset                                                                       |    |

| 3.3.17 XHIF IO driver strength                                                              |    |

| 3.4 ARM926 subsystem                                                                        |    |

| 3.4.1 ARM926EJ-S processor                                                                  |    |

| 3.4.2 Cache structure of the ARM926EJ-S                                                     |    |

| 3.4.3 ARM926 Tightly Coupled Memories (ARM926_TCM)                                          |    |

| 3.4.4 Memory Management Unit (MMU)                                                          |    |

| 3.4.5 Bus interface of the ARM926 processor                                                 |    |

| 3.4.6 ARM926 Embedded Trace Macrocell (ETM9), Trace Buffer (ETB11)                          |    |

| 3.4.7 Debug configuration                                                                   |    |

| 3.4.8 Debug Interface ARM926EJ-S                                                            |    |

| 3.5 ERTEC 200P internal busses                                                              |    |

| 3.5.1 The communication bus (multi-layer AHB)                                               |    |

| 3.5.1.1 AHB arbiter                                                                         |    |

| 3.5.1.2 The AHB master-slave coupling                                                       |    |

| 3.5.2 The I/O bus (APB)                                                                     |    |

| 3.6 Peripherals at the communication bus (multi-layer AHB)                                  | 32 |

| 3.6.1 ARM926 Interrupt Controller (ARM-ICU)                                                 |    |

| 3.6.1.1 Overview                                                                            |    |

|                                                                                             |    |

| 3.6.1.2   | Interface                                     |    |

|-----------|-----------------------------------------------|----|

| 3.6.1.3   | Interrupt aquisition                          |    |

| 3.6.1.4   | Interrupt masking / priorisation              |    |

| 3.6.1.5   | Interrupt post-processing                     |    |

| 3.6.1.6   | Special functions                             |    |

| 3.6.1.7   | Debug functions                               |    |

| 3.6.1.8   | Miscellaneous                                 |    |

| 3.6.1.    |                                               |    |

| 3.6.1.    |                                               |    |

| 3.6.1.    |                                               |    |

|           |                                               |    |

| 3.6.1.    |                                               |    |

| 3.6.1.    | 1                                             |    |

| 3.6.1.9   | Interrupt sources for ARM-IRQ                 |    |

| 3.6.1.10  | · · · · · · · · · · · · · · · · · · ·         |    |

| 3.6.1.11  | Interrupts for accesses to missing addresses  |    |

| 3.6.1.12  |                                               |    |

| 3.6.2 Ho  | st Interrupt Controller                       |    |

| 3.6.3 GE  | DMA – Generic Direct Memory Access Controller |    |

| 3.6.3.1   | DMA: Functional description                   |    |

| 3.6.3.    | 1.1 AHB interfaces                            |    |

| 3.6.3.    | 1.2 Job priorities                            |    |

| 3.6.3.    | •                                             |    |

| 3.6.3.    |                                               |    |

| 3.6.3.    | -                                             |    |

| 3.6.3.    | -                                             |    |

| 3.6.3.    |                                               |    |

| 3.6.3.    |                                               |    |

|           |                                               |    |

| 3.6.3.    |                                               |    |

|           | 1.10 GDMA-IP Bugs                             |    |

|           | ternal Memory Controller (EMC)                |    |

| 3.6.4.1   | EMC-IP Notes                                  |    |

|           | st Interface - parallel (XHIF)                |    |

| 3.6.5.1   | XHIF application information                  |    |

|           | -IP                                           |    |

| 3.6.6.1   | PN-IP Interfaces                              |    |

| 3.6.6.    | 1.1 AHB Interface                             |    |

| 3.6.6.    |                                               |    |

|           | ripheral Interface                            |    |

| 3.6.8 Mu  | Iltiport-Ethernet-PHY                         |    |

|           |                                               |    |

| 3.7 Perip | herals at the I/O bus (APB)                   | 69 |

|           | neral-Purpose-I/Os                            |    |

|           | ilter                                         |    |

| 3.7.2.1   | Principle of the RC filter                    |    |

|           | ner 0 - 5                                     |    |

| 3.7.3.1   | Overview                                      |    |

| 3.7.3.2   | TIMER_TOP functionality                       |    |

| 3.7.3.2   | Timer modul                                   |    |

| 3.7.3.3   | Overview of the counter count modes           |    |

|           |                                               |    |

| 3.7.3.5   | Timing requirements                           |    |

| 3.7.3.6   | Operating rules                               |    |

| 3.7.3.7   | Connections on Toplevel                       |    |

|           | Counter                                       |    |

| 3.7.4.1   | Description of function                       |    |

| 3.7.4.2   | Application information                       |    |

|           | M926 Watchdog                                 |    |

| 3.7.5.1   | Overview                                      |    |

| 3.7.5.2   | Block diagram                                 |    |

| 3.7.5.3   | Signal waveforms                              |    |

| 3.7.5.4   | Write protection of the watchdog register     |    |

| 3.7.5.5   | Starting the Watchdog                         |    |

| 3.7.5.6   | Notes                                         |    |

|           |                                               |    |

| 3.7        | .6 SPI1/2                                                              |     |

|------------|------------------------------------------------------------------------|-----|

| 3.7        | .7 UART1-4                                                             |     |

| 3.7        | .8 l <sup>2</sup> C                                                    |     |

| 2.0        |                                                                        | 00  |

| <b>3.8</b> | General functions                                                      |     |

|            | 3.8.1.1 Cycle generation through PLL                                   |     |

| -          | 3.8.1.2 Cycle supply for the PHYs and the Ethernet MACs                |     |

|            | 3.8.1.3     Cycle supply for JTAG.                                     |     |

|            | .2 Reset system of the ERTEC 200P                                      |     |

|            | 3.8.2.1 Asynchronous PowerOn Reset                                     |     |

|            | 3.8.2.2 Asynchronous Hardware Reset                                    |     |

| 3          | 3.8.2.3 Asynchronous JTAG Reset                                        |     |

| 3          | 3.8.2.4 Asynchronous ARM926 Watchdog-Reset                             |     |

| 3          | 3.8.2.5 Asynchronous Software Reset for the ERTEC 200P                 |     |

|            | 3.8.2.6 Asynchronous Software Reset for the ARM926EJ-S Core            |     |

|            | 3.8.2.7 Synchronous Software Reset (PN-IP, PER-IF, Host Interface)     |     |

| 3.8        | .3 Modules and ASIC code                                               |     |

| 3.9        | Booting the system (boot pins)                                         |     |

| 3.9        |                                                                        |     |

| 3          | 3.9.1.1 NOR Boot Flow                                                  |     |

| 3.9        | .2 Booting via Host Interface                                          |     |

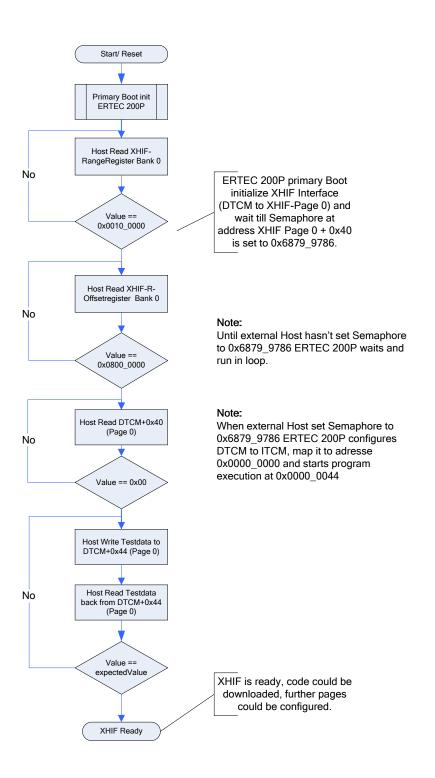

| 3          | 3.9.2.1 XHIF Boot Flow                                                 |     |

| 3.9        | .3 Booting via SPI                                                     |     |

| 3          | 3.9.3.1 SPI Boot Flow                                                  |     |

| 3.9        |                                                                        |     |

| 3.9        | .5 Memory-Swapping                                                     |     |

| 3.10       | Address space and time out monitoring                                  | 112 |

| 3.10       | Address space and time-out monitoring<br>0.1 Monitoring at the AHB end |     |

| 3.1        |                                                                        |     |

| 3.1        |                                                                        |     |

| 3.1        |                                                                        |     |

| 0.1        |                                                                        |     |

| 3.11       | MEM Wrapper                                                            |     |

|            |                                                                        |     |

| 4 1        | HARDWARE INTERFACES                                                    |     |

| 4.1        | Assignment of the function ring                                        | 114 |

| <b>4.1</b> | Assignment of the function pins                                        |     |

| 4.1        |                                                                        |     |

| 4.1        |                                                                        |     |

| 4.1        |                                                                        |     |

| 4.1        | <b>u</b>                                                               |     |

| 4.1        | 1                                                                      |     |

| 4.1        | 1 1                                                                    |     |

|            |                                                                        |     |

| 4.2        | Configuration pins                                                     |     |

| 4.3        | Functional pins                                                        |     |

| 4.4        | Alternate Functions on the GPIO310 and XHIF interface                  |     |

| 4.5        | Setting the Signal Pads (drive strength, pull)                         |     |

| 4.6        | Housing type                                                           |     |

| 4.7        | Pin assignment                                                         |     |

|            |                                                                        |     |

| 5 SOFTWARE INTERFACES                                       |  |

|-------------------------------------------------------------|--|

| 5.1 Memory Mapping                                          |  |

| 5.1.1 Memory Mapping ARM926-I (Instruction AHB interface)   |  |

| 5.1.2 Memory Mapping ARM926-D (Data AHB interface)          |  |

| 5.1.3 Memory Mapping GDMA                                   |  |

| 5.2 Detailled Address Mapping                               |  |

| 5.3 Register-description                                    |  |

| 5.3.1 General information                                   |  |

| 5.3.2 Peripheral Interface                                  |  |

| 5.3.2.1 PERIF_AHB_APP                                       |  |

| 5.3.2.2 PERIF_APB                                           |  |

| 5.3.3 Host Interface                                        |  |

| 5.3.4 Interrupt Controller Unit ARM-ICU                     |  |

| 5.3.5 General DMA Controller - GDMA                         |  |

| 5.3.6 EMC-Register                                          |  |

| 5.3.7 $I^2C$ register                                       |  |

| 5.3.8 System-Control-Register-Block (SCRB)                  |  |

| 5.3.9 UART1-4 register                                      |  |

| 5.3.10 SPI11-2 register                                     |  |

| 5.3.11 Timer 0-5 Register                                   |  |

| 5.3.12 ARM926 Watchdog-Register                             |  |

| 5.3.13 F-Timer-Register                                     |  |

| 5.3.14 GPIO register                                        |  |

| 5.3.15 I-Filter-Register                                    |  |

| 5.4 Detailed ARM Interrupt description                      |  |

| 5.4.1 Interrupts at the ARM Interrupt Controller (IRQ)      |  |

| 5.4.2 Fast-Interrupts at the ARM Interrupt Controller (FIQ) |  |

| 6 MISCELLANEOUS                                             |  |

| 6.1 Directory of abbreviations / terms                      |  |

| 6.2 Literature list                                         |  |

#### **1 OVERVIEW OF THE ERTEC 200P**

The Enhanced Real-Time Ethernet Controller 200P (ERTEC 200P) is a further development of the ERTEC 200. It disposes of a PN-IP with integrated PHYs for high-performance PROFINET communication as well as of an ARM926EJ-S processor for application processing. The mechanisms of the performance upgrade "Fast Forwarding", Dynamic Frame Packing" as well as "Fragmenta-tion" are implemented in the PN-IP. The ERTEC 200P thus allows the development of PROFINET devices with cycle times up to 31.25 µs and isochronous-specific applications. In addition to rapid real-time communication, the ERTEC 200P also allows unlimited access to TCP/IP data and service so that non-time-critical data can be transferred parallel.

Its flexible architecture allows devices to be realized that are both modular and compact. The application of the device can be executed both on the integrated ARM processor of the ERTEC 200P and on an external host CPU. Both applications are described in detail in this documentation as use cases.

The ERTEC 200P is thus suitable for use in a wide range of field device types: Rapid IO peripherals, high-precision measuring instrumentation, synchronous drives and encoders as well as all further types of high-performance and intelligent automation devices

#### 1.1 Switch functions

The term switch functions is used on the one hand for all the functions required for forwarding telegrams by the switch and on the other hand for all the functions used to process data for the user interface.

Through the concept of isochronous real-time Ethernet data traffic via Ethernet is divided into three categories: Depending on the application, TCP/IP, RT or IRT is used for the communication. Because of the required processing of the data by the TCP/IP stack and the unforeseeable runtimes through the network the well-known TCP/IP communication is not suitable for real-time applications in control technology as required by modern control and drive concepts. Operation via RT, that runs on the same switch mechanisms as TCP/IP communication, represents an improvement. In the case of RT an increase in the deterministics of the network is achieved by prioritization of the telegrams and higher throughput is attained by processing the data for the end node..

A further increase in the deterministics is achieved by the transition to IRT traffic in which cyclic communication is executed in reserved time phases. A difference is made between address-based forwarding and topological forwarding.

A further increase in performance is provided by the performance upgrade at IRT that operates on the basis of Fast Forwarding Multicast Address (with Frame ID in Octet 1/2) and uses Pack Frames (bundling of several devices). This reduces the cut through time markedly. A further advantage is the notable reduced cycle times.

#### **1.1.1 IRT communication**

In the case of IRT, cyclic communication runs in reserved time phases. Selection between addressbased forwarding (RTC2) and topological forwarding (RTC3) is possible.

In the case of address-based forwarding the control information required for a telegram transfer only has to be stored at the sender and the receiver. The path is found automatically through the MAC target address.

In the case of topological forwarding the control information required respectively is stored for each individual telegram in **all** the participating nodes, that is in addition to the sender and receiver in all the concerned forwarding nodes. Important advantages are:

- Deterministics in the network through time-driven forwarding of telegrams (prerequisite for this control is a common time base for all the participants of a contiguous real-time Ethernet network)

- Performance of the user interface that is supported by the processing of the user data in process images is supported by the hardware

The ERTEC 200P can also be used as a relative forwarder in simple network topologies.

#### 1.1.2 Performance upgrade at IRT communication

At systems with many participants and particularly high line depths the forwarding time in each individual node becomes a determining factor for the performance. The performance upgrade uses Fast Forwarding (locally administrated MultiCast-Frames with Frame ID in Octet 1/2). This allows every device to already carry out forwarding after the first two bytes of the DA address. Resulting in reduced forwarding time.

Typical field devices in automation technology require only a few process data bytes for cyclic user data transport. PROFINET always requires a complete Ethernet frame with the associated overhead (64 bytes) to transfer these few bytes. To achieve a significant improvement in the performance compared to the current PROFINET, the available band width has to be used better with the performance upgrade. This is achieved by means of Dynamic Frame Packing (DFP). This stores the data of several devices in one frame, the so-called Pack Frame. A so-called "subframe" is assigned to each device for its data. Several "subframes" then form an Ethernet frame.

To allow smaller send cycles the performance upgrade supports TCP/IP fragmentation. Here the switch automatically fragments the TCP/IP frames when necessary.

To allow smaller send cycles the performance upgrade supports TCP/IP fragmentation. Here the switch automatically fragments the TCP/IP frames when necessary.

#### **1.2** System functions

# 1.2.1 Use cases for the ERTEC 200P

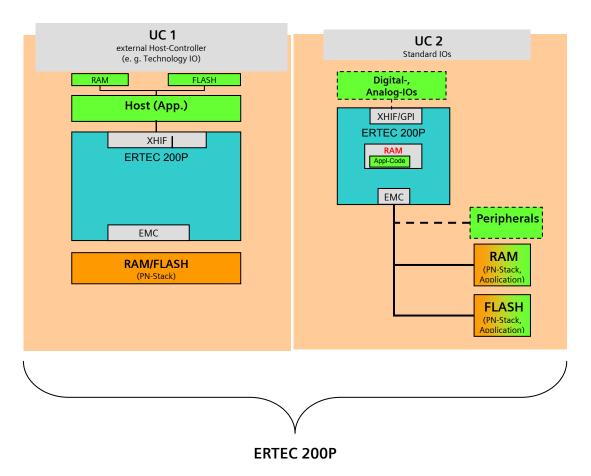

The ERTEC 200P supports 2 use cases (UC1, UC2) that are shown in Figure 1: ERTEC 200P use cases.

Figure 1: ERTEC 200P use cases

# 1.2.1.1 Use case 1 (UC1): Operation with external host

At many devices the communication and the application (technology) are located on separate controllers. This is represented at the ERTEC 200P by the UC1. Only the PROFINET IO stack then runs on the ERTEC 200P. The parallel host interface (XHIF) with 16 or 32 bits can be connected with the external host.

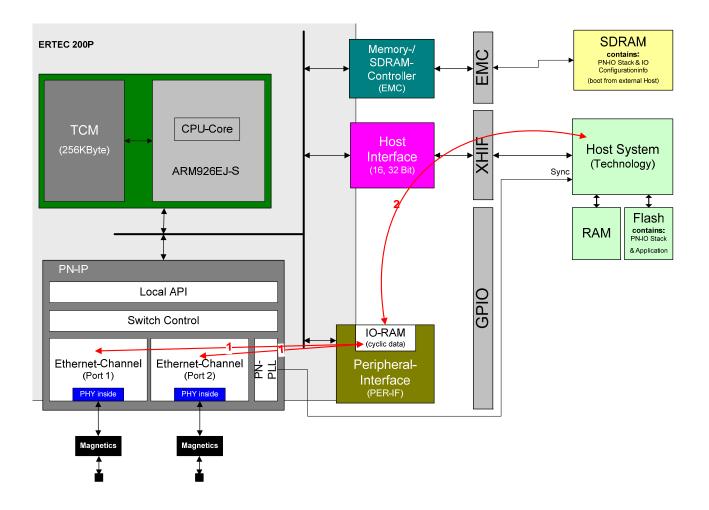

Figure 2: Application operation with external host shows the application with an external host processor. At the ERTEC 200P a SDRAM has to be connected to the memory interface (EMC) in which the PN stack is loaded when the host is boosted.

The acyclic communication data and the configuration data are stored, for example, in the integrated TCM (Tightly Coupled Memory) (256 kbytes) of the ARM926 and the cyclic data in the IO-RAM of the PER-IF. Transfer of the cyclic data (Arrow 1 + 2) is controlled by the PN-IP and by the host. The PN-IP transfers the data into the IO-RAM of the PER-IF. The host then transfers the data from there to its application.

Figure 2: Application operation with external host

At GPIO31:0 outputs from the PLL are available in the PN-IP for synchronous applications on the host. The data transfer to / from the external host is then controlled through these phase signals and corresponding interrupts. If the host has an own PLL for cycle synchronization, these can be synchronized by the PLL of the ERTEC 200P.

# 1.2.1.2 Use case 2 (UC2): Operation without external host

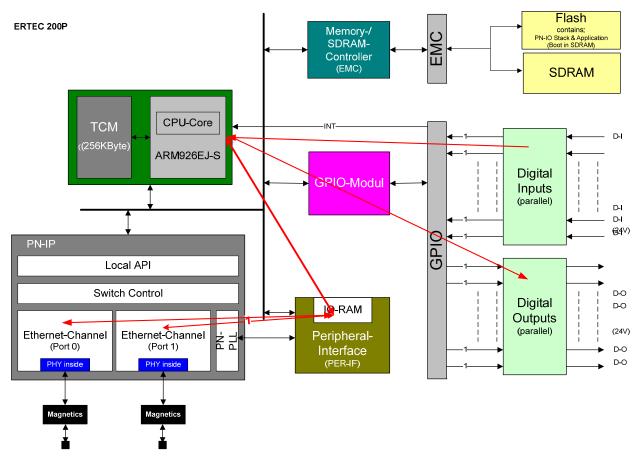

The ERTEC 200P is available for the realization of complex standard IO and remote IO applications with notably more application code. The ERTEC 200P has an external memory interface (flash, SDRAM, SRAM, peripherals) and a small integrated memory (256 kbytes). The PN IO stack and the application lie in the external memory. High-performance acyclic communication data or application code that is to executed rapidly are loaded in the integrated memory of the ERTEC 200P.

The digital and analog IOs are connected to the ERTEC 200P pins. Cyclic data can be controlled by the ARM926 or the GDMA controller via 2x SPI. Alternatively an external bus controller can also be connected via the EMC.

The following profile is supported:

- PN stack and application are combined as sources

- Time-critical application code (<256 kbytes) can be loaded into the integrated RAM

# **Operation without external host**

Figure 3: Application operation without external host shows the application of the standard IO.

Figure 3: Application operation without external host

# 2 SYSTEM FEATURES

#### Manufacturer, technology, enclosure

- Manufacturer: Renesas Electronics

- Enclosure: FPBGA400, 17 mm \* 17 mm

#### **Operating conditions**

| • | Ambient temperature: | -40 to +85°C    |                      |

|---|----------------------|-----------------|----------------------|

| • | Supply voltage IOs:  | EMC interface:  | 1.8 V +5%/-10%       |

|   |                      | Host interface: | 1.8 V/3.3 V +5%/-10% |

|   |                      | GPIO310,:       | 3.3 V +5%/-10%       |

| • | Supply voltage core: |                 | 1.2 V +5%/-0.1 V     |

| • | Supply voltage PHY:  |                 | 1.5 V +5%/-10%       |

| • | Power loss:          | Max. 1.62 W (in | cl. 2x int. PHY)     |

#### **Processor system**

- Integrated processor system ARM926EJ-S (frequency 125/250 MHz)

- 16 kbyte Data and 16 kbyte Instruction Cache

- 256 kbyte Instruction/Data Tightly Coupled Memory incl. Byte EDC, adjustable in 64 kbyte steps (I-TCM: 0 256 kbytes, D-TCM: 256 0 kbytes)

- Debug capability through embedded ICE with JTAG interface, ETM cell with ETB (Embedded Trace Buffer)

- Memory Management Unit (MMU)

#### **Bus structure**:

- Internal 32-bit structure

- Multi-layer architecture with parallel access structure multi-master to multi-slaves (125 MHz)

- 16/32-bit bus interface to external SDRAM/SRAM/flash and external peripherals

#### **PN-IP:**

- 2 Ethernet ports with integrated PHYs (100 Mbits, full-duplex)

- IRT to 31.25 μs cycle time, IRT, RT and TCP/IP data traffic

#### Interfaces:

- EMC (External Memory Controller) 1.8 V

- (Mobile) SDRAM (125 MHz)

- Asynchronous SRAM interface (4 Chip-Select areas, Ready-Control) Burst Flash Interface

- XHIF (External Host Interface) 1.8 V / 3.3 V

- Interface for external host

- 16-/32-bit data width

- GPIO: GPIO31-0 with 16 I-filters, GPIO95-32 with 64 I-filters parallel

- $1 \times I^2 C$

- $1 \times I^2 C$  (in the PN-IP for POF transceivers)

- 4x UART

- 2x SPI1 (master / slave)

#### **General functions:**

- Internal cycle generation (quartz oscillator, PLL)

- Integrated boot ROM (8 kbytes)

- 6 x Timers

- Watchdog

- F-counter

- GDMA controller

- ARM926 interrupt controller

#### Test function:

Boundary Scan

#### **3 HARDWARE STRUCTURE**

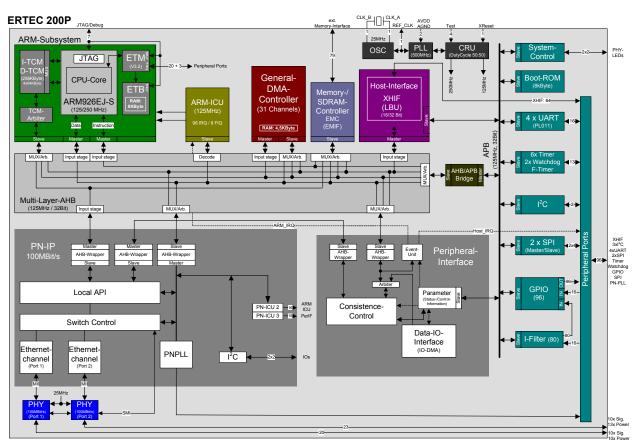

#### 3.1 Block diagram ERTEC 200P

Figure 4: ERTEC 200P block diagram

# 3.2 Overview of the ERTEC 200P IP utilization

| IP                              | Used by the<br>PROFINET<br>stack | Usable by the application | Note                                                                                                                   |  |

|---------------------------------|----------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| ТСМ                             | no                               | yes                       | -                                                                                                                      |  |

| => nicht im TCM ARM926          | yes                              | yes                       | -                                                                                                                      |  |

| ETM                             | no                               | yes                       | For Debugging purposes                                                                                                 |  |

| ETB                             | no                               | yes                       | For Debugging purposes                                                                                                 |  |

| ARM-ICU                         | yes                              | yes                       | Details see clause 3.6.1.9                                                                                             |  |

| General-DMA-Controller          | no                               | yes                       | -                                                                                                                      |  |

| Host-Interface                  | -                                | yes                       | *1)                                                                                                                    |  |

| System-Control (SCRB)           | yes                              | yes                       | The System-Control Register Block<br>contains the registers which are<br>used by the application and<br>PROFINET Stack |  |

| System-Control (Phy-LEDs)       | yes                              | no                        | -                                                                                                                      |  |

| Boot-ROM                        | n/a                              | n/a                       | -                                                                                                                      |  |

| UARTs (1-4) (@APB)              | no                               | yes                       | -                                                                                                                      |  |

| F-Timer (@APB)                  | no                               | yes                       | -                                                                                                                      |  |

| 2x Watchdog (@APB)              | no                               | yes                       | see also Application notes, clause 3.3.13                                                                              |  |

| 6x Timer (@APB)                 | Timer 0                          | Timer 1-5                 | Timer 0 is used by the operation system of the Evaluation Kit                                                          |  |

| I2C (@APB)                      | no                               | yes                       | -                                                                                                                      |  |

| 2x SPIs (APB)                   | no                               | yes                       | -                                                                                                                      |  |

| GPIO (GPIO31-0)                 | yes                              | yes                       | The following GPIOs are used by the Evaluation Kit ERTEC 200P:                                                         |  |

|                                 |                                  |                           | GIO0: SyncOut                                                                                                          |  |

|                                 |                                  |                           | GPIO9: SyncIn                                                                                                          |  |

|                                 |                                  |                           | GPIO25-31: LEDs                                                                                                        |  |

| GPIO (GPIO95-32)                | no                               | yes                       | -                                                                                                                      |  |

| I-Filter (@APB)                 | no                               | yes                       | -                                                                                                                      |  |

| Peripherie-Interface            | yes                              | yes                       | -                                                                                                                      |  |

| Peripherie-Interface (Host-IRQ) | no                               | no                        | 1*)                                                                                                                    |  |

| PN-IP                           | yes                              | no                        | -                                                                                                                      |  |

| I2C (@PN-IP)                    | yes                              | no                        | -                                                                                                                      |  |

|                                 | luation Kit ERTEC                | 200P. Please refer        | sion of the PROFINET stack version<br>to the User Interface Description of                                             |  |

# Table 1: Overview of the ERTEC 200P IP utilization

#### 3.3 Application notes

The user should pay attention to the following application notes:

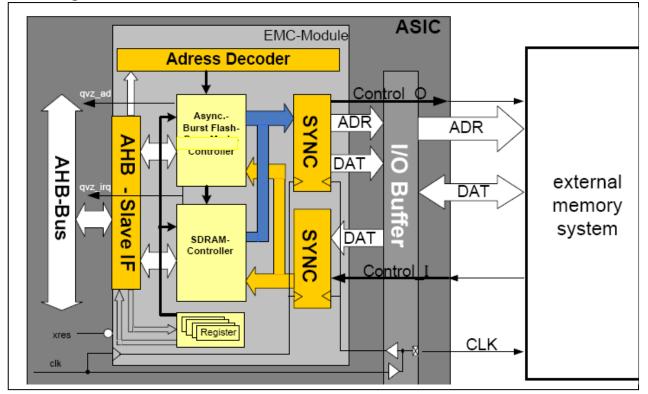

#### **3.3.1 EMC SDRAM-Interface**

The EMC of the ERTEC 200P offers two setting options for the cycled signal output (address, data and control signals) to an externally connected SDRAM that can be configured using Bit (27) in the Extended\_Config register (see Chapter 5.3.6):

• Extended\_Config(27)= '0': SDRAM signal output with feedback clock at the pin

CLK\_I\_SDRAM (register value after reset)

• Extended\_Config(27)= '1': SDRAM signal output with internal system cycle

(value required for correct operation!)

⇒ The reset value of the register bit **must** be reconfigured to **Extended\_Config(27) = '1'** here in the ERTEC 200P for correct SDRAM timing.

#### 3.3.2 EMC BurstFlash-Interface

The EMC of the ERTEC 200P offers two setting options for the cycled signal output (XAV\_BF) to an externally connected BurstFlash that can be configured using Bit (26) in the Extended\_Config register (see Chapter 5.3.6

• Extended\_Config(26)= '0': BurstFlash signal output with feedback clock at the pin

CLK\_I\_BF (register value after reset)

• Extended\_Config(26)= '1': BurstFlash signal output with internal system cycle

#### (value required for correct operation!)

⇒ The reset value of the register bit **must** be reconfigured to **Extended\_Config(26) = '1'** here in the ERTEC 200P for correct BurstFlash timing.

The EMC of the ERTEC 200P offers two setting options for the selection of the operating frequency of an externally connected BurstFlash that can be configured using Bit (0) in the BF\_Config register (see Chapter 5.3.6):

- BF\_Config(0)= '0': Half rate BF with 62.5 MHz (register value after reset)

- BF\_Config(0)= '1': Full rate BF with 125 MHz (value is not supported in ERTEC 200P!)

⇒ The reset value of the register bit BF\_Config(0) = '0' must be retained here in the ERTEC 200P for correct BurstFlash timing!

#### **3.3.3 I-/D-TCM Mapping register of the ARM926 subsystems**

The ARM926 subsystem is equipped with a TCM block (256 kbytes) whose distribution between I-TCM for Code and D-TCM for Data can be set using a mapping register.

⇒ The I-/D-TCM mapping register of the ARM926 subsystem (SCRB register bits TCM926\_MAP(2:0), see Chapter 5.3.8 and Chapter 3.4.3) may be switched over during operation at ERTEC 200P, if it is ensured that the ARM926 is not accessing the I-/D-TCM at the switching-over moment, meaning that neither Code nor Data access is being carried out on it.

This can be achieved by executing the code from an external RAM, such as the SDRAM, at the switching-over moment.

# 3.3.4 I-TCM accesses of the ARM926 with 250MHz

Accesses of the ARM926 to the I-TCM are exclusively accomplished by the ARM-Core and scale with the configured cycle rate (see clause: 3.4.3).

⇒ At the ERTEC 200P the performance of the I-TCM accesses are not scalable with the cycle rate. The performance is equal regardless if 250MHz or 125MHz are used. Reason: At a cycle rate of 250MHz the accesses to the I-TCM are accomplished with one wait state.

The access to the Cache-Memory scales with the clock rate of the ARM926 therefore the performace at 250MHz is higher than with 125MHz.

#### **3.3.5** Accesses to the IO-RAM in the Peripherie-Interface (Per-IF)

The IO-RAM in the Per-IF can be accessed by different AHB-instances (ARM926, XHIF, GDMA) and also from the PN-IP. The Per-IF supports burst and single accesses from the AHB side. The corresponding operation mode has to be set in the Burst\_Config register (see 5.3.2.2).

- ⇒ For proper operation, burst accesses from the application AHB-instances ARM926, XHIF and GDMA to the IO-RAM in the Per-IF are not allowed. Therefore the default values in the Burst\_Config register shall be changed from the default values (burst access) to single access as follows:

- Set Burst Config.BurstMode  $comAHB(1dto0) = '0b01' (default) \rightarrow '0b11'$

- Set Burst Config.BurstMode applAHB(9dto8) = '0b01' (default) → '0b00'

Note: With this PerIF settings the PerIF Interrupt *CR\_State\_comErr\_INT* can be triggered wrongly and should be ignored. This interrupt is for debug purposes only. Per default all interrupts in the PerIF registers *Host\_IRQmask\_low* and *PN\_IRQmask\_low* are masked.

# 3.3.6 Trigger of GDMA HW-Jobs by GPIOs 0...3 is not supported

The GDMA supports jobs which can be triggered by different sources, like Timer, PNPLL and GPIOs 0...3.

$\Rightarrow$  The trigger of GDMA jobs by the GPIOs 0...3 is not supported.

# **3.3.7** Acknowledgement of the PN-ICU3 accumulative interrupts in the Event-Unit of the PerIF

The PN-ICU3 in the PN-IP provides 16 interrupts (2 accumulative interrupts and 14 individual interrupts) for the Event-Unit in the PerIF. The accumulative interrupts are provided only level triggered, therefore the interrupt service routine has to take care about the acknowledgment of these interrupts.

⇒ For the acknowledgment of the 2 accumulative PN-ICU3 interrupts the interrupt service routine has at first to acknowledge the interrupts at the PN-ICU3 and after that the interrupt service routine can acknowledge the accumulative interrupts in the Event-Unit at the PerIF.

# 3.3.8 AHB Burstbreaker

The values of the burst length of the ARM926I- and ARM926D-AHB-Master-Interface should be changed from the default values (burst breaker deactivated) to 8, see also clause 5.3.8.

- Set AHB\_BURSTBREAKER. NR\_ADDR\_ARM926\_D(7dto0) = '0x00' (default) → '0x08'

- Set *AHB\_BURSTBREAKER*. *NR\_ADDR\_ARM926\_I(15dto8)* = '0x00' (*default*) → '0x08'

# **3.3.9 XSRST function at active XRESET**

The XSRST signal (JTAG interface) is combined with the CTRL-STBY function (ERTEC 200P pin: CTRL\_STBY0).

If the CTRL-STBY function is activated, the related output signals will be set in tristate (high impedance).

If the XRESET signal is connected with the CTRL\_STBY0 pin (on the PCB), the ERTEC 200P pin XSRST will be set in tristate if the XRESET signal is activated. In this case the signalling of the active XRESET signal to the debugger is not possible.

⇒ The debugger has to recognize an actvie XRESET signale by different means and shall perform a reset. In the normal operation mode (XRESET signal is not active) a reset of the ERTEC 200P via the XSRST signal of the debugger is still possible, see also clause 3.8.2.3

# 3.3.10 EDC reporting

To improve system reliability ERTEC 200P memories are EDC (Error Detection and Correction) protected (1Bit Error is correctable, 2Bit Error are detectable).

EDC protected RAMs need an initialization, which is done by hardware at startup; status is indicated in register EDC INIT DONE.

This feature is enabled by default and could be disabled for ARM TCMs by setting EDC\_PARITY\_EN register for other RAMs it could not disabled.

If an EDC error is detected on ARM TCMs an Undefined Instruction Exception (ITCM) or Undefined Data Exception (DTCM) is generated, if other RAMs are hit IRQ48 (EDC\_Event) is asserted and register EDC\_EVENT must be checked for source.

An interrupt service routine for IRQ48 (EDC\_Event) must be setup on ARM926 to handle this error.

Note: When disabling TCM EDC logic, FIT rate regarding SoftError-Rate exceed the specified value >1000FIT@2000m.

# 3.3.11 Cache-Parity-Check

I-/ D-Cache and associated Tag RAM are parity protected. The feature must be enabled <u>after</u> initialization of caches by setting I\_CACHE\_PAR\_EN = 1 and D\_CACHE\_PAR\_EN = 1 in register EDC\_PARITY\_EN. Additional an interrupt service routine for IRQ48 (EDC\_Event) must be setup on ARM926 to handle this error.

# 3.3.12 Access Error

ERTEC 200P has an internal access monitors, which observes accesses to memory gaps on EMC-, AHB-, APB-bus and TCMs. Following interrupts on ARM926 ICU will be generated:

- IRQ53 (QVZ\_EMC\_ADR) when an EMC Address Error occurs

- IRQ52 (QVZ\_APB\_ADR) when an APB Address Error occurs

- IRQ51 (QVZ\_AHB\_ADR) when an AHB Address Error occurs

The error address and additional information (master of access, type ...) are latched up in SCRB QVZ register for further handling.

Additional some modules have also an internal access monitor, which observes access to register gaps. If such an access happens, IRQ86 is generated and MODUL\_ACCESS\_ERR register hold detailed information about

Finally TCM memories have a separated monitoring. If there are accesses to TCM memory gaps following interrupt will generated:

- IRQ88 when access to gap in I-TCM ARM926 occurs

- IRQ89 when access to gap in D-TCM ARM926 occurs

Care must be taken to handle all these ISR.

#### 3.3.13 ARM926 Watchdog

Watchdog timer should be used to prevent a hardware fault or program error.

#### 3.3.14 PLL LOCK

At startup the software should check that PLL is locked by checking LOCK flag in PLL\_STAT\_REG register.

#### 3.3.15 PLL LOSS

ERTEC 200P has an internal PLL monitor; when PLL is out of specified range IRQ49 is generated. An interrupt service routine must be setup on ARM926 to handle this error.

#### 3.3.16 Software Reset

For faster startup after ARM926 software reset primary bootloader will jump directly to RETURN\_ADDRESS specified in RES\_SOFT\_RETURN\_ADDR.

*Note: The RETURN\_ADDRESS in RES\_SOFT\_RETURN\_ADDR register has to be set, otherwise an exception (fetch code from* 0x00000000) *will generated.*

#### 3.3.17 XHIF IO driver strength

If XHIF interface operates at 1,8V; driver strength hat to be set to 9mA (register DRIVE47 32GPIO, DRIVE63 48GPIO, DRIVE79 64GPIO and DRIVE95 80GPIO).

#### 3.4 ARM926 subsystem

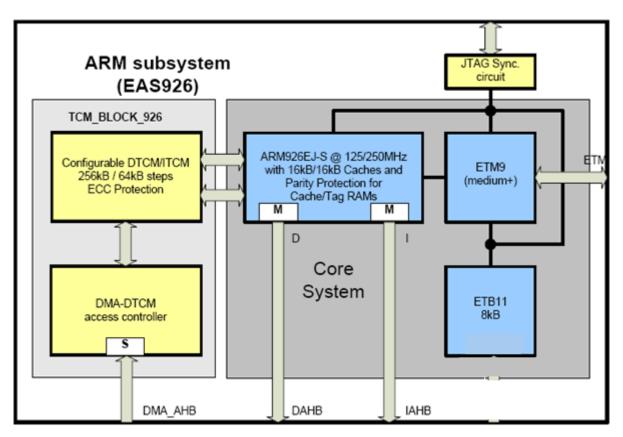

An ARM926 subsystem is used. The ARM926 subsystem is mainly available for the application and the non-runtime-critical routines of the PN stack. Figure 5: ARM926 subsystem shows the structure of the ARM926 subsystem. It consists of a core system, the JTAG interface and a TCM\_Block\_926. In addition to the ARM926EJ-S processor the core system contains a Data and an Instruction Cache, a Memory Management Unit (MMU), separate interfaces to the respective AHB layers for instruction and data, a trace macro cell ETM9 (medium+). The Tightly Coupled Memories for data and instruction are located in the TCM\_Block\_926. AHB access to the D-TCM is effected through a 'DMA-DTCM Access Controller'. The I-TCM is only operated from the ARM926EJ-S and cannot be reached by the AHB. The ARM926EJ-S is described in detail under /7/.

Of the AHB masters the PN-IP, Host Interface and the GDMA can access the D-TCM in the ARM926 subsystem. The ARM926EJ-S has access to all the AHB slaves.

Figure 5: ARM926 subsystem

# 3.4.1 ARM926EJ-S processor

The ARM926EJ-S revision r0p5 contains an ARM9E-S processor core with Harvard architecture. This processor core has the improved v5TE architecture in contrast to the ARM9 processor core of the ARM9TDMI. These improvements mainly apply to the points improved "ARM/Thumb interworking" (faster changing between ARM and Thumb Code segments) and improved Multiplier Structure. In addition to the processor core the ARM9E-S has an Embedded ICE Logic RT. This logic unit is controlled through the integrated JTAG interface. Document /9/ describes the interfacing of the Embedded ICE Interface Connector to the ERTEC 200P (reset, JTAG connector , etc.). A detailed description of the ARM9E-S is available in /6/.

The processor and the TCMs (see Chapter 3.4.3) can be operated with 125 MHz or 250 MHz. Configuration is carried out through the CONFIG(1) pin (see Chapter 4.2). The AHB interfaces always run at 125 MHz.

The ARM926EJ-S can only be operated in little endian mode.

The following bit has to be set at the ARM926EJ-S core in order to recognize "Unaligned Access":

• CP15 register c1 (Control Register), set bit 1 (A-bit) to enable fault checking of address alignment..

# 3.4.2 Cache structure of the ARM926EJ-S

The functional scope of the cache of the ARM926 can be described by the following properties:

- 16 kbytes Instruction Cache

- 16 kbytes Data Cache

- "write buffer" for write-back function of the Data Cache

- Caches are 4 way set associative caches with 1 kbyte segments

- A segment consists of 32 lines and each line contains 32 bytes (meaning 8 words).

The content can be locked at the cache segments. This lock functionality makes it possible to keep the command set for rapid routines permanently in the I Cache. This mechanism can only be carried out segment-granularly at the .ARM926EJ-S. Further information about caching is available in /7/.

If a time-out (QVZ) interrupt occurs an an I Cache Refill through an AHB Error (caused. for example, by a WRAP8 at the memory end), <u>no</u> Prefetch Abort Exception is triggered at the ARM926EJ-S. The allocation to the faulty word is no longer possible for the ARM due to I Cache. However, it is advisable to configure the MMU correspondingly so that an exception to the ARM926EJ-S is generated in this case. In this case an MMU Exception is triggered when the memory area is left.

The I- and D-Cache has a byte parity. The I- and D-Tag RAM is also parity-protected. If an error occurs while reading on the I-Cache or the corresponding I-Tag entry, the error cause (I\_Cache\_Parity, I\_Tag\_Parity) is stored in the SCRB register 'EDC Event' (see Chapter 5.3.8) and the interrupt 'EDC\_Event' IRQ48 is triggered (see Chapter 5.4.1). An error while reading on the D-Cache or the corresponding D-Tag entry causes the entry (D\_Cache\_Parity, D\_Tag\_Parity) in the 'EDC Event Register' with the interrupt 'EDC\_Event'. To delete the EDC Event Register has to be overwritten with '0h'.

After a reset the parity bits are undefined. The software has to initialize the caches (each cache line has to be initialized in a loop). Up to this moment the parity logic is disabled. Control is carried out through the SCRB register 'EDC\_PARITY\_EN' (see Chapter 5.3.8). The 'I\_CACHE\_PAR\_EN Bit' enables the parity bits of the I-Cache and I-Tag and the 'D\_CACHE\_PAR\_EN Bit' enables the parity bits of the D-Cache and the D-Tag. After a reset both bits are set to '0' and the parity bits are disabled. After the cache initialization the software has to set these bits to '1'.

# 3.4.3 ARM926 Tightly Coupled Memories (ARM926\_TCM)

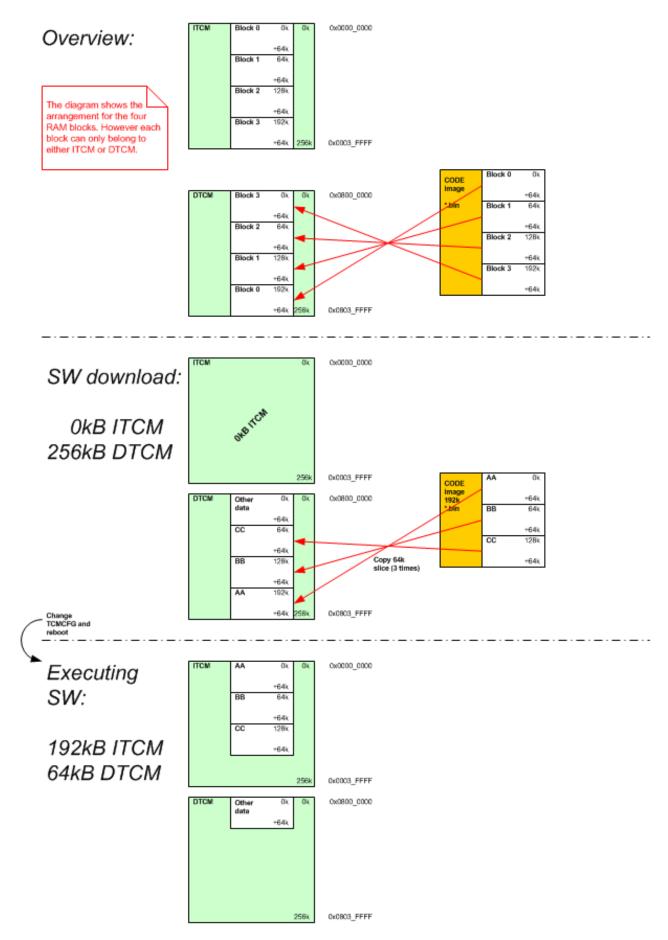

The I- and D-TCM are located in the TCM\_Block\_926. The TCM configuration encompasses 256 kbytes for Instruction and Data TCM (I/D-TCM). The memory operates with the cycle rate of the processor 125/250 MHz. The memory consists of segments of 64 kbytes that can be assigned to either the Instruction or the Data TCM. This results in a configurable memory

24

size of 0 - 256 kbytes for the I-TCM at 256 - 0 kbytes for the D-TCM. After the reset the TCM926 configuration is set to 256 kbytes D-TCM. The final settings is carried out during booting by the Bootloader (software) in the SCRB register 'TCM926\_Map' (see Chapter 5.3.8). After this reconfiguration the bootloader still has to display the TCM memories in the coprocessor interface (CP15 c9) in the address area (see Chapter 5.1.1, 5.1.2). Note that the I-TCM and D-TCM can only be displayed in the address area in a size of  $2^n$  steps. If, for example, a physical size of I-TCM = 192 kbytes / D-TCM = 64 kbytes was selected in 'TCM926\_Map Register', the ARM926 can only assign an address area of 256 kbytes to the I-TCM and the desired address area of 64 kbytes to the D-TCM. The values 256 kbytes for I-TCM and 64 kbytes for D-TCM are therefore to be read out in the coprocessor interface of the ARM926 (CP15 c9).

The software may then not access the unassigned area / hole (I-TCM: 192 – 256 kbytes). If access is carried out in the unassigned area from ARM926, either the 'Invalid I-TCM926 Access Interrupt' (access in the hole of I-TCM) or the 'Invalid D-TCM926 Access Interrupt' (access in the hole of D-TCM) is triggered (see Chapter 5.4.1).

Unpredictable accesses in the I/D-TCM hole can <u>not</u> be intercepted by the ARM926, the 'Invalid I/D-TCM926 Access Interrupt' is generated. The situation can be mastered if the MMU codes out the hole and 'Invalid I/D-TCM926 Access Interrupt' is blocked. The MMU does not see any unpredictable accesses.

In the implementation an address area of 256 kbytes is assigned respectively for the I-TCM and the D-TCM. This ensures all the possible combinations of the distribution between I-TCM and D-TCM. After the insertion the I-TCM lies in the ARM926 address area from  $0x0000\_0000h$  and the D-TCM from  $0x0800\_0000h$ . Further information about the TCMs is available in /7/.

Only the ARM926 D\_TCM can be reached from the AHB. If an access into the unassigned range of D-TCM is carried out from an AHB master, access is prevented and a time-out (QVZ) interrupt is triggered (see Chapter 3.10.1).

AHB access to the D-TCM is effected through the 'DMA-DTCM Access Controller'. The I-TCM is only served by the ARM926EJ-S and cannot be accessed by the AHB.

The boot process for the I-TCM is effected as follows:

In the boot ROM a primary bootloader runs that loads a secondary bootloader from the boot medium into the D-TCM in such a manner that after the switchover to the I-TCM the secondary bootloader is located behind the interrupt entry table. If an external host is responsible for booting, it transfers the secondary bootloader into the D-TCM.

After the secondary bootloader has been loaded, this 64 kbyte segment is switched over to the I-TCM. The loaded secondary bootloader is not lost during the changeover to the I-TCM. Figure 6 shows the course of the loading of a code image into the D-TCM (for example secondary bootloader). After the PowerOn Reset the TCM926 configuration is set to 256 kbytes D-TCM. Since the assignment of the SRAM blocks in the I-TCM and D-TCM memory is completely twisted, the bootloader has to fill up the code image in 64 kbyte blocks from the lower D-TCM block upwards. The address order is not twisted in the respective TCM block. After the download to the D-TCM the final TCM926 configuration is set in the TCM926\_MAP register (see Chapter 5.3.8). Subsequently the bootloader has to insert the TCM memories in the coprocessor interface (CP15 c9) into the address area.

The primary bootloader then hands over to the loaded secondary bootloader in which the user then continues the application-specific booting process. One task of the secondary bootloader is to fill a code images into the I-TCM. Two options are available to this purpose:

- The secondary bootloader sets the final required TCM926 configuration in the TCM926\_MAP register (see Chapter 5.3.8). Afterwards the code image can be transferred from the boot medium into the I-TCM behind the secondary bootloader.

- First the 64 kbyte segment that is already assigned to the I-TCM is filled completely. Afterward the code image is loaded further into the D-TCM in the correct order (see Figure 6). After the download to the D-TCM the final TCM926 configuration is set in the TCM926\_MAP register (see Chapter 5.3.8). The secondary bootloader still has to also insert the final configuration of the TCM memories into the coprocessor interface (CP15 c9) into the address area.

The GDMA can also be used to load the code image into the D-TCM. In the case of a booting process from the host it will load the code image into the D-TCM.

The primary bootloader has to set up a page on the D-TCM (boot RAM) in the 8 page registers of the XHIF for booting from an external host. The remaining pages can subsequently be set up specifically by the external host. It is advisable to lay further pages on the PN-IF, PER-IF, EMC-SDRAM / EMC-SRAM, GMDA and APB Peripherals.

Figure 6: Booting the I-TCM ARM926EJ-S

The I- and D-TCM is provided byte-by-byte with an EDC code (5 bits per byte, 1Bit Error correctable, 2Bit Error recognizable). If an error occurs while reading, the error cause (I/D-TCM926-1B: 1Bit Error corrected or I/D-TCM926-2B: 2Bit Error recognized) is stored in the SCRB register 'EDC\_EVENT' (see Chapter 5.3.8) and the interrupt 'EDC\_Event' IRQ48 is triggered (see Chapter 5.4.1). To delete the EDC Event Register has to be overwritten with '0h'.

After the ARM926-TCM reset (assignment see Figure 29: Reset matrix of the ) an initialization of the complete TCM is carried out automatically by the hardware. The initialization process for the complete I-/D-TCM amounts to approx. 16.5  $\mu$ s. Completion of this initialization is signaled in the SCRB Register 'EDC\_INIT\_DONE' (see Chapter 5.3.8) (I\_TCM926\_INIT\_DONE, D\_TCM926\_INIT\_DONE). The EDC logic can also be disabled through the SCRB Register 'EDC\_PARITY\_EN' (see Chapter 5.3.8). The bit 'EDC\_DISABLE\_ARM926' disables the EDC logic, but the EDC logic always have to be activ. After the reset the EDC logic is enabled.

The D-TCM can be written and read by the AHB masters (PN-IP, Host Interface, GDMA). During access by one of these masters to the D-TCM the ARM is stalled (pipeline halted). As a rule this stall lasts only one processor cycle per word transfer to carry out the transfer from the 'DMA-DTCM Access Controller' (part of the ARM926 subsystem) to the D-TCM and vice versa. Arbitration is carried out in round-robin scheduling, meaning that the accesses to the D-TCM are always carried out alternatively by the ARM and the 'DMA-DTCM Access Controller'. A new arbitration is also carried out at a burst transfer after every single access.

| EAS 926 , 250 MHz                         |                     | access types       |                                   |                                  |                                |                                |                        |                                 |                          | Description:                                                   |  |

|-------------------------------------------|---------------------|--------------------|-----------------------------------|----------------------------------|--------------------------------|--------------------------------|------------------------|---------------------------------|--------------------------|----------------------------------------------------------------|--|

| Memory area                               | AHB write<br>access | AHB read<br>access | AHB read getting<br>an ECC detect | AHB read getting<br>an ECC error | TCM write<br>access            | TCM read<br>access             | TCM read<br>ECC detect | TCM read<br>ECC error           | ok                       | no error                                                       |  |

| ITCM area<br>(from AHB not possible)      | na1                 | na1                | na1                               | na1                              | ok                             | ok                             |                        | I-TCM926-1B<br>+<br>I-TCM926-2B | na1                      | not availiable /<br>access is not possible                     |  |

| ITCM area hole<br>(from AHB not possible) | na1                 | na1                | na1                               | na1                              | Invalid I-<br>TCM926<br>Access | Invalid I-<br>TCM926<br>Access | na2                    | na2                             | na2                      | not availiable /<br>access never issues an<br>ECC detect/error |  |

| ITCM area mirror<br>(not possible)        | na1                 | na1                | na1                               | na1                              | na1                            | na1                            | na1                    | na1                             | AHB error<br>D-TCM926-1B | AHB error response<br>via HRESP<br>AHB ECC detect signal       |  |

| DTCM area                                 | ok                  | ok                 | D-TCM926-1B                       | D-TCM926-1B<br>+<br>D-TCM926-2B  | ok                             | ok                             | D-TCM926-1B            | D-TCM926-1B<br>+<br>D-TCM926-2B | D-TCM926-2B              | AHB ECC error signal<br>8ns width for the DTCM                 |  |

| DTCM area hole                            | na1                 | na1                |                                   | na1                              | Invalid D-<br>TCM926<br>Access | Invalid D-<br>TCM926<br>Access |                        | na2                             | I-TCM926-1B              | AHB ECC detect signal<br>8ns width for the ITCM                |  |

| DTCM area mirror<br>(not possible)        | na1                 | na1                | na1                               | na1                              | na1                            | na1                            | na1                    | na1                             | I-TCM926-2B              | AHB ECC error signal<br>8ns width for the ITCM                 |  |

Table 2 lists the various ARM926EJ-S access types with the possible errors I./D-TCM and the AHB:

Table 2: ARM926EJ-S Access types to I-/D-TCM / AHB

# 3.4.4 Memory Management Unit (MMU)

The MMU (see ARM926EJ-S Technical Reference Manual /7/) supports a 'demand page virtual memory' system which is required by operating systems such as Linux or eCos depending on the application. The MMU contains the access protection mechanisms for all the memory accesses. The address translation, the access protection and the region type are stored in a TLB (Translation Lookaside Buffer). Separate TLBs are available for Instruction and Data. These TLBs are automatically evaluated or updated respectively by the MMU hardware.

- Page size: 1 Mbyte, 64 kbytes, 4 kbytes and 1 kbyte

- Separate TLBs for Instruction and Data

- Access attributes can be changed without a TLB Flush

- Fast Context Switch allows a virtual address remapping in a range of 0 32 Mbytes

- TLB entries can be locked

The MMU RAMs do not have a parity!

# 3.4.5 Bus interface of the ARM926 processor

The ARM926 processor has a separate AHB interface for Opcode fetches (ARM926-I) and data transfers (ARM926-D). The interfaces operate with 125 MHz. The databus and address bus width amounts to 32 bits each. The data bus interface operates via a "write buffer" (16-step FIFO). When the "write buffer" is used, data write sequences are transferred to the "write buffer" and the data unit of the processor can continue processing immediately. Further information about the bus interface and about the "write buffer" is available in /7/.

# 3.4.6 ARM926 Embedded Trace Macrocell (ETM9), Trace Buffer (ETB11)

For debug support an ETM9 revision r2p2 (medium+ module with integrated trace buffer (ETB11), that allows an Instruction and Data trace, is activated in the ERTEC 200P at the ARM926EJ-S system. The trace buffer has a size of 2Kx32 bits and supports both ARM926 clocks (125 / 250 MHz).

The ETM module receives all the signals necessary for the Data and Instruction trace from the processor. The ETM9 module is operated through the JTAG interface. The trace information is entered via an FIFO in the internal trace buffer.

Only the half-rate mode is supported as the clock mode. In this case the trace clock runs at half the processor frequency (62.5 MHz at 125 MHz processor cycle) and the trace data have a maximum change frequency of 125 MHz. The debugger accepts the data with both trace clock edges.

A detailed description of the ETB11 and the corresponding programming interface is provided in the document 'ETB11 Technical Reference Manual (ARM DDI0275B)' /46/.

# 3.4.7 Debug configuration

2 TAP controllers are circuited in the JTAG chain (see also Chapter 3.4.8):

- TAP#0: ETB from ARM926EJ-S

- TAP#1: ARM926EJ-S

This results in the following chain:

•  $TDI \rightarrow ETB \rightarrow ARM926EJ-S \rightarrow TDO$

The number of 'Instruction Register Bits' amounts to (see Figure 7):

- IR-Length ETB: 4 bits

- IR-Length ARM926EJ-S: 4 bits

Figure 7: JTAG chain

#### 3.4.8 Debug Interface ARM926EJ-S

Only external debuggers with JTAG interface are supported.

To this purpose the pin 'CHAIN\_CTRL' is defined as the VDD supplier. The JTAG interface encompasses the standard signals (XTRST, TCK, TDI, TMS, TDO and XSRST). In addition the RTCK Clock output is made available. A JTAG cycle rate of TCK = 32 MHz is possible for debuggers that support RTCK. Otherwise the maximum cycle rate only amounts to TCK = 16 MHz.

The two signals DBGREQ and DBGACK are furthermore supported via the JTAG interface for the ARM926EJ-S. When DBGREQ is active, the external debugger forces the ARM926EJ-S directly into the debug state. DBGACK active signals the debugger that the ARM926EJ-S is in the debug state. Both signals lie as an alternate function on the GPIO31-0 pins. Before these debug signals can be used, they have to be enabled in the GPIO31-0 block. If DBGREQ is not enabled in its alternate function, DBGREQ is switched inactive internally and the ARM926EJ-S is not in the debug state.

#### **3.5 ERTEC 200P internal busses**

The ERTEC 200P has 2 internal bus systems. These are a high-performance communication bus (multi-layer AHB) and an I/O bus (APB).

All 6 masters (ARM926-I, ARM926-D, PN-IP-M1, IRT PN-IP-M2, GDMA Controller, Host Interface) and the slaves (D-TCM926, Interrupt-Controller (ARM-ICU), GDMA-Register/Memory, External Memory Controller (EMC), APB Bridge, Peripheral Interface (2 connections) and PN-IP are connected directly to the multi-layer AHB that is characterized by a high data transmission rate and bus availability.

Through an AHB/APB bridge the masters can access the remaining peripherals that are connected to a low-performance I/O bus (APB). The AHB/APB bridge is the only master at the I/O bus.

#### 3.5.1 The communication bus (multi-layer AHB)

The multi-layer AHB bus is a 32-bit-wide multi-master-compatible bus. It runs with 125 MHz and has the functionality of the ARM AHB Lite bus.

6 AHB masters can access various slaves simultaneously by switching together several AHB segments in the "multi-layer AHB" (see Chapter 3.1).

In the case of simultaneous access by several masters to one slave an arbiter decides to which master this slave is assigned.

Due to the multi-layer architecture there is no retry functionality at the AHB (AHB Lite). Similarly the split functionality is not supported (AHB Lite).

The lock functionality can be enabled for the the ARM master (ARM926-D) in the SCRB Register  $M\_LOCK\_CTRL$ . By default the lock functionality is disabled. The ARM926-I master cannot generate a lock.

The APB module allows the following access:

| AHB-module (Slave)    | allowed access | note            |

|-----------------------|----------------|-----------------|

| PN-IP                 | 8/16/32 bit    | databus: 32 bit |

| Peripherie-Interface  | 8/16/32 bit    | databus: 32 bit |

| EMC Memory            | 8/16/32 bit    | databus: 32 bit |

| EMC Register          | 8/16/32 bit    | databus: 32 bit |

| GDMA (RAM + Register) | only 32 bit    | databus: 32 bit |

| ARM-ICU               | only 32 bit    | databus: 32 bit |

| ARM926 - TCM          | 8/16/32 bit    | databus: 32 bit |

#### 3.5.1.1 AHB arbiter

Each of the AHB arbiters uses the same arbitration process. By default round-robin is set. A fixed priority assignment of the AHB masters (see 5.3.8) can be set as an alternative arbitration algorithm by programming the bit ARB\_MODE in the SCRB Register M\_LOCK\_CTRL (see Table 3). However, this should not be done in view of the dynamic processes at the multilayer AHB.

With round robin as the arbitration process reciprocal blocking of the AHB masters at the multi-layer AHB is prevented for a longer period (see Section3.5.1.2).

| PRIORITIES | MASTER         | REMARKS          |

|------------|----------------|------------------|

| 6          | Host Interface | Highest priority |

| 5          | GDMA           |                  |

| 4          | PN-IP-M1       |                  |

| 3          |                |                  |

| 2          | ARM926-D       |                  |

| 1          | ARM926-I       | Lowest priority  |

Table 3: Fixed priority assignment (no default)

#### 3.5.1.2 The AHB master-slave coupling

The respective masters are not connected with all slaves within the "multi-layer AHB". The following table shows which AHB master is connected with which AHB slave.

| AHB-Master                      | D-TCM<br>926 | ARM-<br>ICU | GDMA | EMC | APB | PER-<br>Host | PER-<br>PN | PN-IP |

|---------------------------------|--------------|-------------|------|-----|-----|--------------|------------|-------|

| ARM926-D<br>(AHB Burst Breaker) |              | Х           | Х    | Х   | Х   | Х            |            | Х     |

| ARM926-I<br>(AHB Burst Breaker) |              |             |      | Х   | Х   |              |            |       |

| GDMA                            | Х            |             | Х    | Х   | Х   | Х            |            |       |

| Host Interface                  | Х            |             | Х    | Х   | Х   | Х            |            | Х     |

| PN-IP-M1                        | Х            |             |      | Х   |     |              |            |       |

| PN-IP-M2                        |              |             |      |     |     |              | Х          |       |

#### Table 4: AHB master slave coupling

#### Note:

The AHB masters may not keep a slave arbitrated for too long to ensure that long blockades do not occur during access to a slave. This could happen, for example, when the ARM926-D master has too many transactions to the EMC slave in its write buffer. Another master (for example Host Interface or PN-IP-M1) would be blocked for this time in accessing the EMC

slave and would have to wait in wait mode until the ARM926-D master releases the EMC slave again.

The ARM926-D and ARM926-I masters have a burst breaker at the AHB access that enforces an idle phase for a clock after a number of consecutive address phases that has to be configured. In this idle phase a different AHB master can the access the AHB slave. This is possible because rearbitration at an AHB slave can only be carried out when a master enables this AHB slave (idle phase). As the burst breaker is disabled per default, the application has to enable the burst breaker, see application note, claus 3.3.8.

#### <u>Note:</u> All the AHB participants operate in Little-endian mode.

# 3.5.2 The I/O bus (APB)

The APB bus is a 32-bit-wide bus. The bus frequency amounts to 125 MHz. The APB bus in the ERTEC 200P has an extended functionality compared to the ARM APB bus (see Chapter 3.7). Compared to the standard APB bus it provides the option of using variable timing (Wait-states) and byte enables. The waitstate and byte enable capability is attained by inserting sideband signals. This makes is possible to also access peripherals byte-by-byte.

Only the AHB/APB bridge has master functionality on the APB. All the peripheral blocks of the APB are operated as a slave.

The AHB/APB bridge has a one-level write buffer.

| APB-modul             | allowed access | note                                                   |  |  |  |  |

|-----------------------|----------------|--------------------------------------------------------|--|--|--|--|

| SCRB                  | only 32 bit    | databus: 32 bit                                        |  |  |  |  |

| Boot-ROM              | 8/16/32 bit    | databus: 32 bit                                        |  |  |  |  |

| Host-Interface (XHIF) | only 32 bit    | databus: 32 bit                                        |  |  |  |  |

| UART                  | 16/32 bit      | databus: 16 bit, i.e. the upper 16 bit will be ignored |  |  |  |  |

| F-Timer               | only 32 bit    | databus: 32 bit                                        |  |  |  |  |

| Timer 0-5             | only 32 bit    | databus: 32 bit                                        |  |  |  |  |

| Watchdog              | only 32 bit    | databus: 32 bit                                        |  |  |  |  |

| I2C                   | 8/16/32 bit    | databus: 8 bit, i.e. the upper 24 bit will be ignored  |  |  |  |  |

| SPI                   | 16/32 bit      | databus: 16 bit, i.e. the upper 16 bit will be ignored |  |  |  |  |

| GPIO                  | only 32 bit    | databus: 32 bit                                        |  |  |  |  |

| I-Filter              | 8/16/32 bit    | databus: 32 bit                                        |  |  |  |  |

| Peripherie-Interface  | 8/16/32 bit    | databus: 32 bit                                        |  |  |  |  |

# The APB module allows the following access:

# 3.6 Peripherals at the communication bus (multi-layer AHB)

The function blocks connected to the AHB all have 32-bit-wide interfaces.

# **3.6.1** ARM926 Interrupt Controller (ARM-ICU)

# 3.6.1.1 Overview

The Interrupt Controller Unit (ICU), supports both IRQ (Interrupt Request) and FIQ (Fast Interrupt Request) interrupt levels which are named in the following IRQ subblock and FIQ subblock. This overview Chapter describes the functionality using the IRQ subblock. The following sections discuss the differences between the IRQ subblock and the FIQ subblock.

The Interrupt Controller Unit both in the IRQ subblock and in the FIQ subblock consists of three functional units described in detail in the following sections.

The following overview provides an impression of the operation of the ICU:

- 1. The specific preprocessing for each interrupt is performed in the first functional unit of the IRQ subblock. This preprocessing includes:

- Enable and disable of interrupts

- Settings for trigger modes

- Processing of software interrupts, etc.

When an interrupt event occurs at the ICU input, this preprocessing is performed initially before the interrupt is entered in the Interrupt Request Register (IRREG, can be read by the software).

- 2. The second functional unit is responsible for decoding the priorities (priority resolving) for each interrupt. It is determined in each clock:

- Whether a pending interrupt will be forwarded to the third functional unit

- If several interrupts are pending, which of these have the highest priority.

- 3. This interrupt (or its priority) is compared in the third functional unit (postprocessing, ICU-ISR) with any interrupt currently being processed by the software (using the priority).

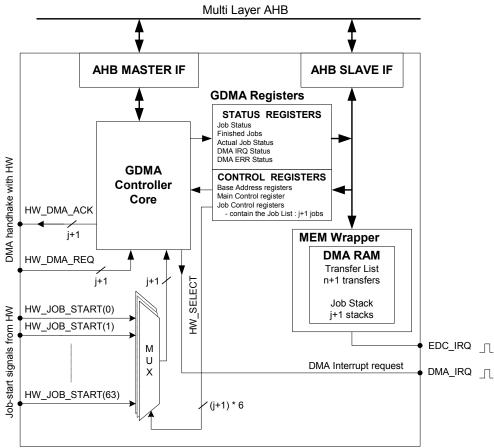

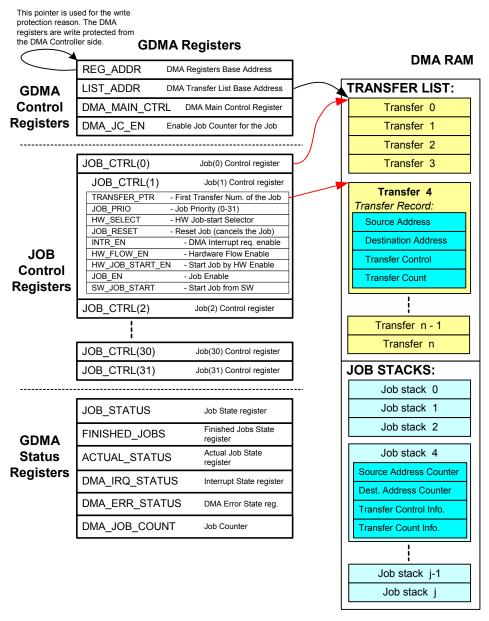

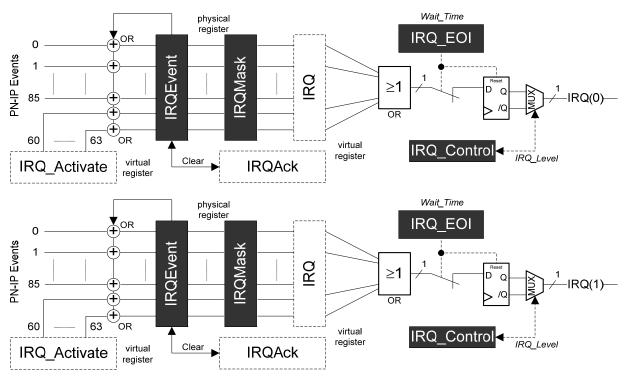

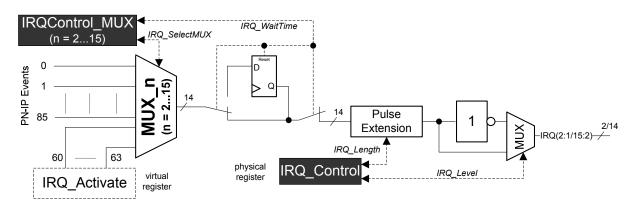

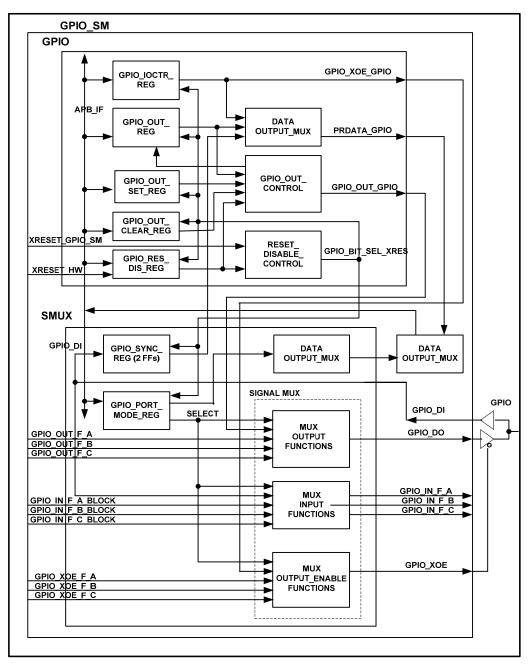

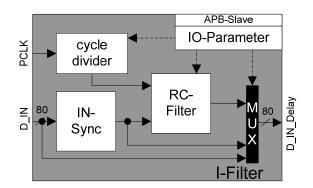

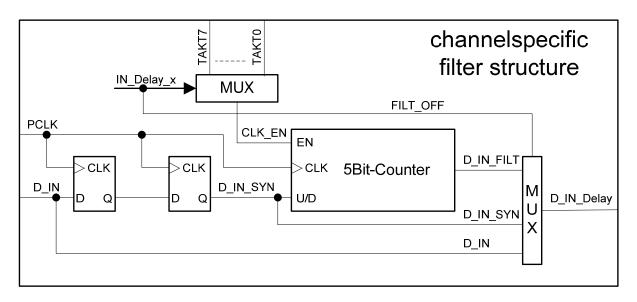

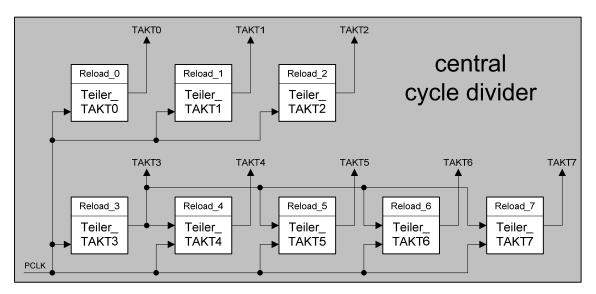

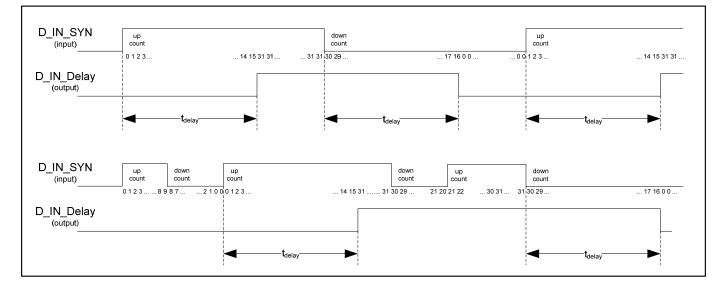

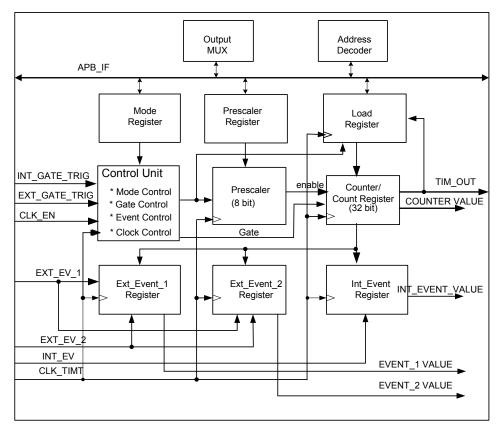

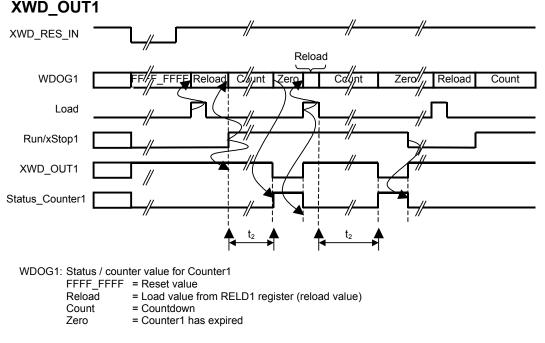

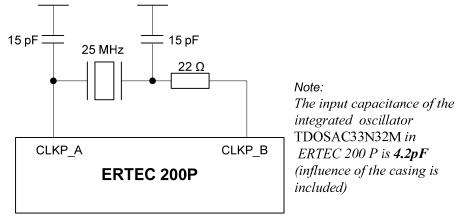

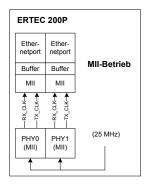

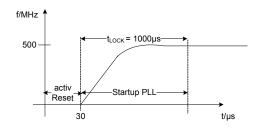

- If the pending interrupt is valid, namely has the appropriate priority, it will be reported to the CPU.