# SINUMERIK 810 Basic Version 2 SINUMERIK 820

**PLC Programming**

Planning Guide

Manufacturer

Documentation

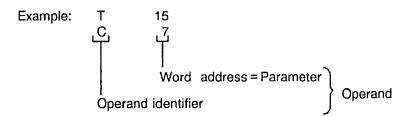

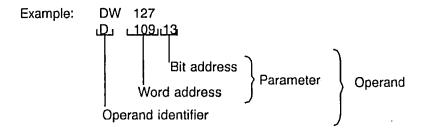

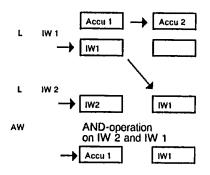

10.90 Edition

#### SINUMERIK 810, Basic Version 2 (GA 2) **General Documentation** SINUMERIK 810/820 810M 810T Accessories 810M 810T SINUMERIK SINUMERIK SINUMERIK SINUMERIK SINUMERIK Catalog NC 90 **Technical Data** Catalog NC 21 Catalog NC 22 Sales Brochure **User Documentation** 800 810T GA2 810M GA2 SINUMERIK **SINUMERIK** SINUMERIK Contour Calculator User's Guide for NC Geometry (Operating/Programming) **Programs Manufacturer Documentation** 800 GA2 820 800 800 810TGA2 810 GA2 SINUMERIK SINUMERIK SINUMERIK 3/8/800 SINUMERIK SINUMERIK SINUMERIK SINUMERIK WS 800 PLC Programming Measuring Cycles: Universal Interface Instructions Manual Interface: General CL 800 Language - Signals - Cables and Turning Milling Connections **Service Documentation** 810 GA2 SINUMERIK I SINUMERIK SIROTEC Spare Parts List Installation Guide

InstructionsLists

# SINUMERIK 810 Basic Version 2 SINUMERIK 820

# **PLC Programming**

# **Manufacturer Documentation**

**Planning Guide**

| Control                      | Software version |

|------------------------------|------------------|

| SINUMERIK 810T/ 810TE (GA 2) | 2                |

| SINUMERIK 810M/ 810ME (GA 2) | 2                |

| SINUMERIK 810N/ 810NE        | 1                |

| SINUMERIK 810G/ 810GE        | 1                |

| SINUMERIK 820T/ 820TE        | 2                |

| SINUMERIK 820M/ 820ME        | 2                |

| SINUMERIK 820N/ 820NE        | 1                |

| SINUMERIK 820G/ 820GE        | 1                |

**October 1990 Edition**

#### SINUMERIK® documentation

#### **Printing history**

Brief details of this edition and previous editions are listed below.

The status of each edition is shown by the code in the "Remarks" column.

Status code in "Remarks" column:

**A...** New documentation **B...** Unrevised reprint with new Order No.

C... Revised edition with new status

| Edition | Order No.           | Remarks |

|---------|---------------------|---------|

| 05.89   | 6ZB5 410-0BX02-0BA0 | Α       |

| 10.90   | 6ZB5 410-0BX02-0BA1 | С       |

Other functions not described in this documentation might be executable in the control. This does not, however, represent an obligation to supply such functions with a new control or when servicing.

This publication was produced on the Siemens 5800 Office System.

Subject to change without prior notice.

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

## **Preliminary Remarks**

Notes to the reader

This manual is intended for the manufacturers of machine tools using SINUMERIK 810 (basic version 2) and SINUMERIK 820.

The Guide describes in detail the program structure and the operation set of the PLC, and explains precisely how basic PLC software and user programs, which comprise data blocks, function blocks and organization blocks, are constructed.

The SINUMERIK documentation is organized in three levels:

- User documentation

- Manufacturer documentation and

- Service documentation

The Manufacturer Documentation for SINUMERIK 810 basic version 2 (GA2) and SINUMERIK 820 is divided into the following:

- Instruction Manual

- Interface

- Part 1: Signals

- Part 2: Cables and hardware

- PLC Programming Guide

Additional SINUMERIK publications are also available for all SINUMERIK controls (e. g. publications on the Universal Interface, Measuring Cycles, CL 800 Cycles language).

Please contact your Siemens regional office for further details.

Technical Information

| Introductory Remarks                                  |   |

|-------------------------------------------------------|---|

| Program Blocks                                        |   |

| Data Blocks                                           |   |

|                                                       |   |

| Function Blocks                                       | [ |

| Organization Blocks                                   |   |

| Integral Function Blocks                              |   |

| Transfer Parameters and Operating System Machine Data |   |

| Error Analysis                                        |   |

| STEP 5 Command Set with Programming Examples          |   |

| Rules of Compatibility                                |   |

## **Contents**

|                                         |                                                                                                                                      | Page                            |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1                                       | Introductory Remarks                                                                                                                 | 1-1                             |

| 1.1                                     | Application                                                                                                                          | 1-1                             |

| 1.2                                     | STEP 5 Programming Language                                                                                                          | 1-2                             |

| 1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4 | Programming                                                                                                                          | 1-3<br>1-3<br>1-4<br>1-5<br>1-6 |

| 2                                       | Program blocks                                                                                                                       | 2-1                             |

| 2.1                                     | Programming Program Blocks                                                                                                           | 2-1                             |

| 2.2                                     | Calling Program Blocks                                                                                                               | 2-2                             |

| 3                                       | Data blocks                                                                                                                          | 3-1                             |

| 3.1                                     | Programming Data Blocks                                                                                                              | 3-1                             |

| 3.2                                     | Calling Data Blocks                                                                                                                  | 3-2                             |

| 4                                       | Function blocks                                                                                                                      | 4-1                             |

| 4.1                                     | General Remarks                                                                                                                      | 4-1                             |

| 4.2<br>4.2.1<br>4.2.2                   | Structure of Function Blocks                                                                                                         | 4-2<br>4-2<br>4-2               |

| 4.3<br>4.3.1<br>4.3.2                   | Calling and Initializing Function Blocks Call statement Parameter list                                                               | 4-3<br>4-3<br>4-3               |

| 4.4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4 | Programming Function Blocks Library number  Name of the function block  Formal operand (block parameter name)  Block parameter types | 4-4<br>4-4<br>4-5<br>4-6        |

| 5                                       | Organization Blocks                                                                                                                  | 5-1                             |

| 5.1                                     | General Remarks                                                                                                                      | 5-1                             |

| 5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | Cyclic scanning Interrupt capability Response time and scan time Programming the cyclic program Interface between operating system and cyclic program Basic program organization | 5-2<br>5-2<br>5-3<br>5-3<br>5-4<br>5-5 |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| 5.3<br>5.3.1<br>5.3.2<br>5.3.3                   | Interrupt Processing                                                                                                                                                             | 5-7<br>5-7<br>5-7<br>5-8               |  |

| 6                                                | Integral Function Blocks                                                                                                                                                         | 6-1                                    |  |

| 6.1                                              | General Remarks                                                                                                                                                                  | 6-1                                    |  |

| 6.2                                              | FB Identifiers                                                                                                                                                                   | 6-2                                    |  |

| 6.3                                              | Function macros                                                                                                                                                                  | 6-3                                    |  |

|                                                  | FB 11 EINR-DB Generate data blocks                                                                                                                                               | 6-4                                    |  |

|                                                  | FB 60 BLOCK-TR Block transfer                                                                                                                                                    | 6-6                                    |  |

|                                                  | FB 61 NCD-LESE Read NC data FB 62 NCD-SCHR Write NC data                                                                                                                         | 6-8                                    |  |

|                                                  | FB 65 M→STACK Transfer flags to stack                                                                                                                                            | 6-20                                   |  |

|                                                  | FB 66 STACK →M Flag stack to transfer flag area                                                                                                                                  | 6-21                                   |  |

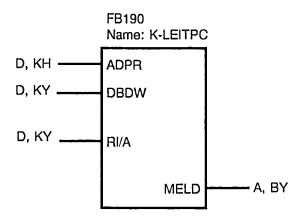

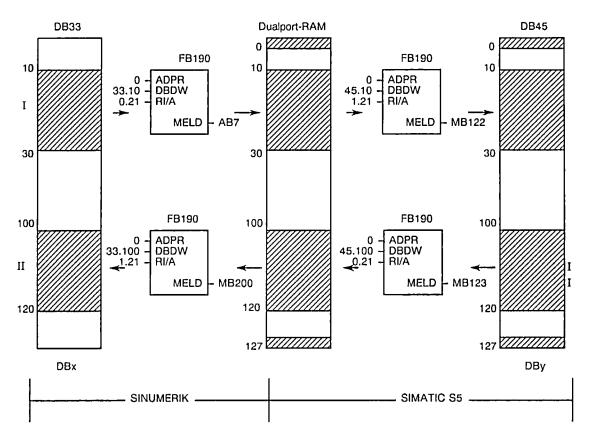

|                                                  | FB 190 K - LEITPC Signal interchange with master PLC                                                                                                                             | 6-22                                   |  |

| 7                                                | Transfer Parameters and Operating System Machine Data                                                                                                                            | 7-1                                    |  |

| 7.1                                              | Transfer Parameters                                                                                                                                                              | 7-1                                    |  |

| 7.2                                              | PLC Machine Data SINUMERIK 810 basic version 2/ 820                                                                                                                              | 7-3                                    |  |

| 7.3                                              | PLC Machine Data Bits SINUMERIK 810 basic version 2/ 820 7-4                                                                                                                     |                                        |  |

| 8                                                | Error Analysis                                                                                                                                                                   | 8-1                                    |  |

| 8.1                                              | Types of Error                                                                                                                                                                   | 8-1                                    |  |

| 8.2                                              | Interrupt Stack                                                                                                                                                                  | 8-2                                    |  |

| 8.3<br>8.3.1<br>8.3.2                            | Detailed Error Code                                                                                                                                                              | 8-5<br>8-5<br>8-7                      |  |

| 8 <b>4</b>                                       | Alarm List                                                                                                                                                                       | 8-8                                    |  |

| 9                                                                                                                                      | STEP 5 command set with programming examples                                                                                                                                                                                                                                                                                                                                                                                      | 9-1                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 9.1<br>9.1.1<br>9.1.2                                                                                                                  | Memory organization                                                                                                                                                                                                                                                                                                                                                                                                               | 9-1<br>9-3<br>9-3                                                                                    |

| 9.2<br>9.2.1<br>9.2.2<br>9.2.3                                                                                                         | General notes                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-4<br>9-4<br>9-6<br>9-7                                                                             |

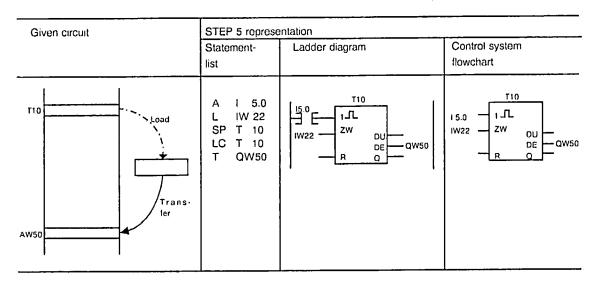

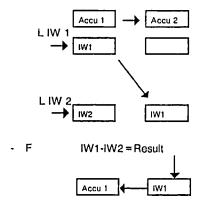

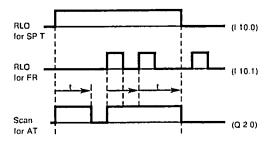

| 9.3<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>9.3.7<br>9.3.8<br>9.3.9                                                   | Basic operations Logic operations, binary Storage operations Load and transfer operations Timing and countingoperations Comparison operations Block calls Code operations Arithmetic operations Other operations                                                                                                                                                                                                                  | 9-9<br>9-12<br>9-15<br>9-17<br>9-26<br>9-30<br>9-32<br>9-33<br>9-34                                  |

| 9.4<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6<br>9.4.7<br>9.4.8<br>9.4.9<br>9.4.10<br>9.4.11<br>9.4.12<br>9.4.13<br>9.4.14 | Supplementary operations (FB only) Logic operations, binary Setting operations Timing and counting operations Enabling operations for timing and counting operations Bit test operations (FB, FX only) Load and transfer operations Logic operations, digital Shift operations Conversion operations Decrementing / Incrementing Jump operations Processing operations STEP 5 commands with direct memory access Other operations | 9-34<br>9-35<br>9-35<br>9-36<br>9-38<br>9-39<br>9-40<br>9-41<br>9-42<br>9-42<br>9-43<br>9-46<br>9-48 |

| 9.5                                                                                                                                    | Rules of compatibility between the LAD, CSF and                                                                                                                                                                                                                                                                                                                                                                                   | 9-50                                                                                                 |

| 10.1                                                                                                                                   | STL methods of representation                                                                                                                                                                                                                                                                                                                                                                                                     | 10-1                                                                                                 |

| 10.2                                                                                                                                   | Rules of compatibility for graphic program input (LAD, CSF)                                                                                                                                                                                                                                                                                                                                                                       | 10-2                                                                                                 |

| 10.3                                                                                                                                   | Rules of compatibility for program input in a statement list                                                                                                                                                                                                                                                                                                                                                                      | 10-4                                                                                                 |

## 1 Introductory Remarks

## 1.1 Application

The PLC is a powerful interface controller. It has no inherent hardware, and is used as "Software PLC" exclusively in the SINUMERIK 810 basic version 2 (GA 2) and SINUMERIK 820.

The PLC is responsible for control of machine-related functional sequences such as

- Controlling auxiliary axes

- Controlling tool-changers

- Gathering the signals generated by the machine's monitoring devices.

#### Special features:

On the SINUMERIK 810 basic version 2, all NC and PLC jobs are executed by a common processor (Intel 80 186). A specially developed coprocessor (COP) is responsible for high-speed execution of binary operations in the STEP 5 user program (e. g. A I 3.0, S Q 8.1, etc.). The single-processor structure calls for strict priority scheduling of NC and PLC jobs. NC functions such as position control and block preparation, but also the PLC "Interrupt processing" function (OB 2), have highest priority, while scanning of the cyclic program (OB 1) is of less importance. The amount of processor time available to the PLC has been restricted to a maximum of 20% in order to ensure that the NC can fulfill its primary objectives (positioning accuracy, short block change times) even in extreme situations, e. g. where an exceptionally long STEP 5 program or frequent interrupt servicing is involved. It is also possible to influence the manner in which the cyclic user program scanned via machine data (see Section 1.3.4).

## 1.2 STEP 5 Programming Language

The operations available in STEP 5 enable the user to program functions ranging from simple binary logic to complex digital functions and basic arithmetic operations.

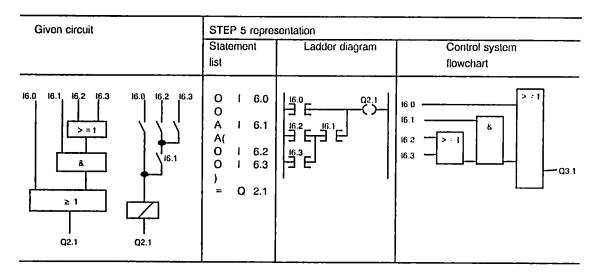

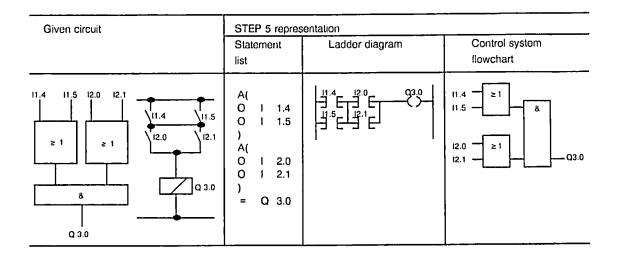

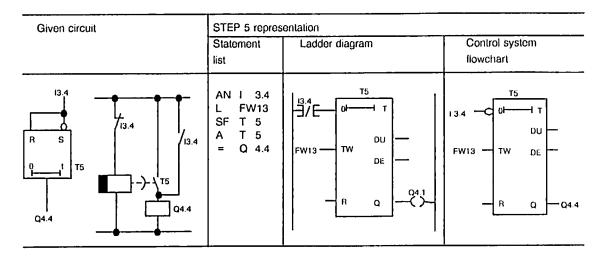

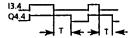

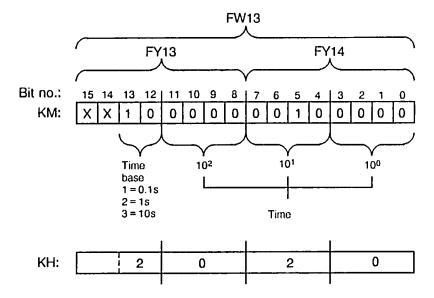

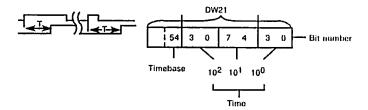

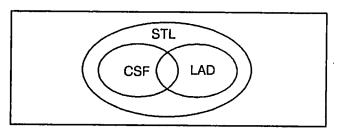

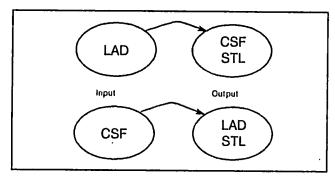

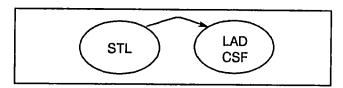

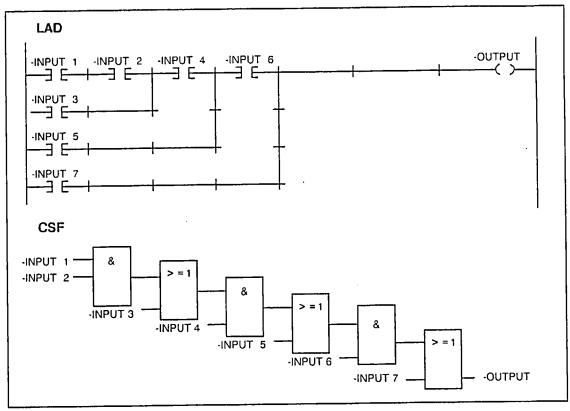

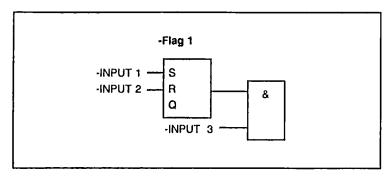

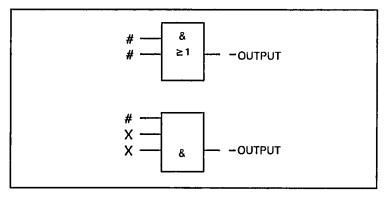

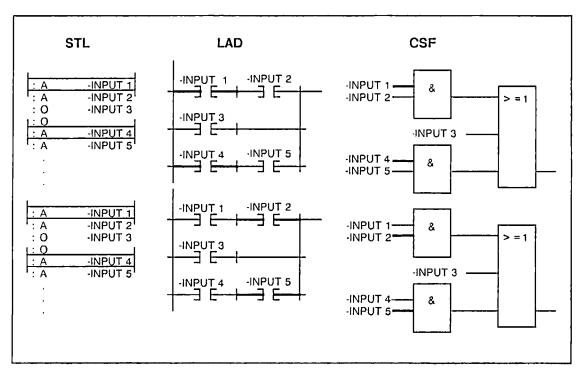

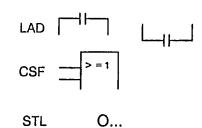

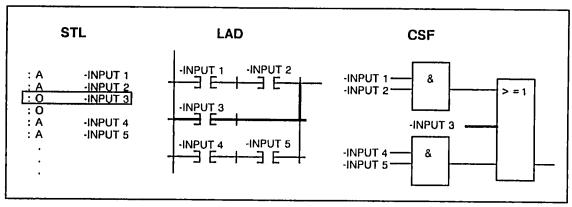

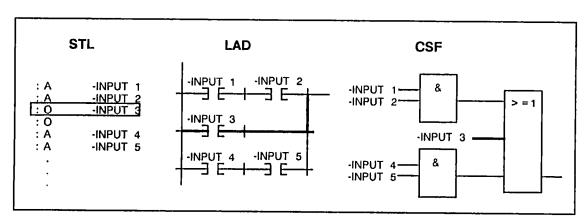

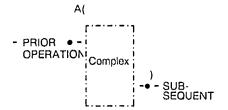

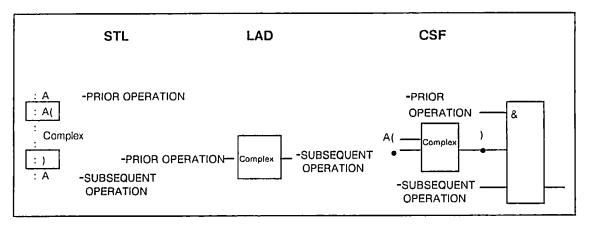

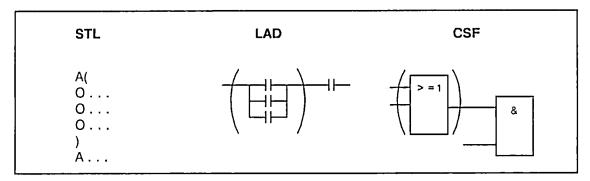

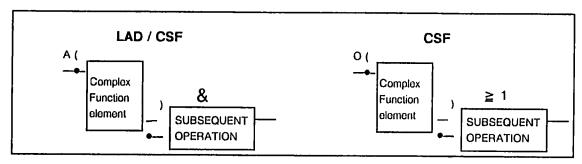

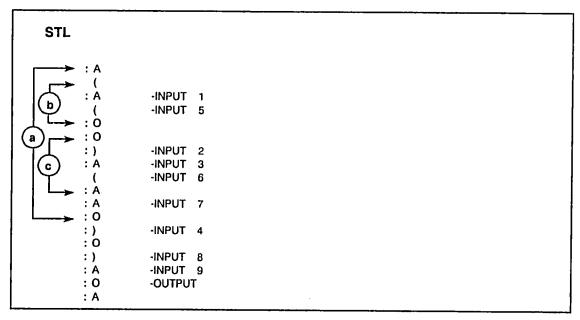

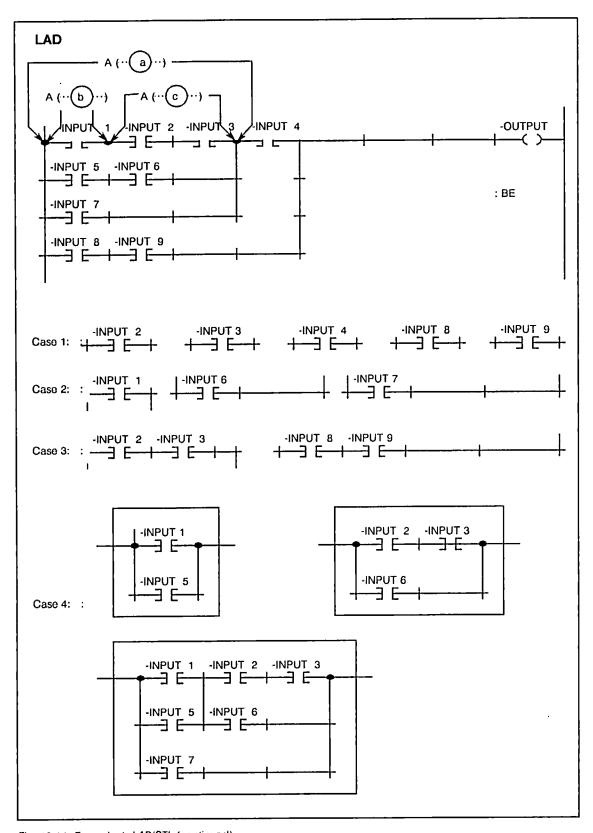

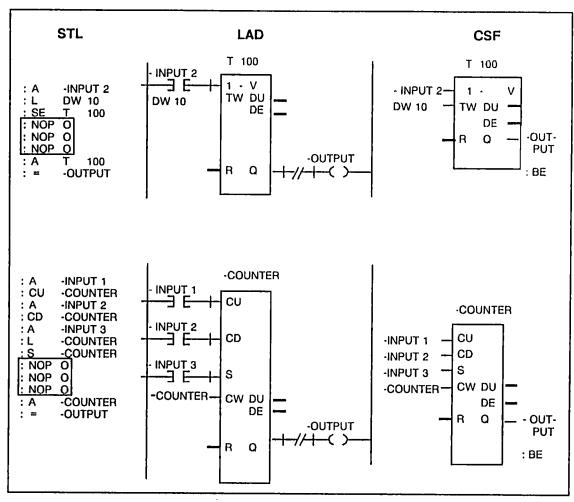

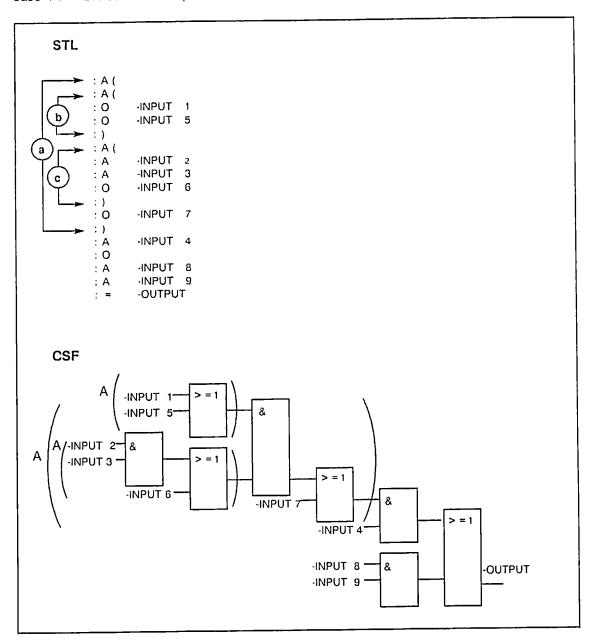

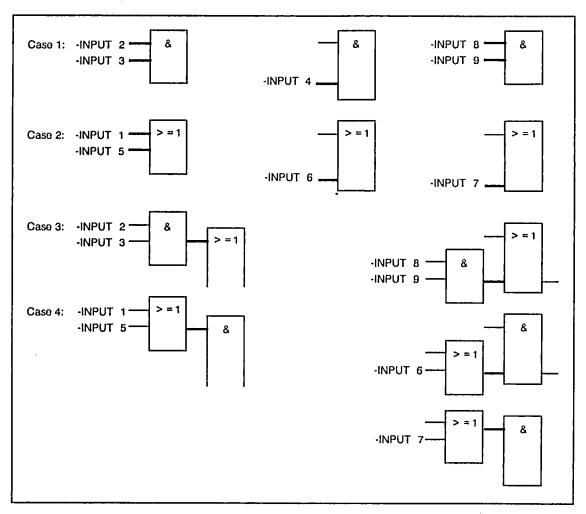

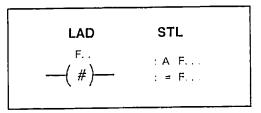

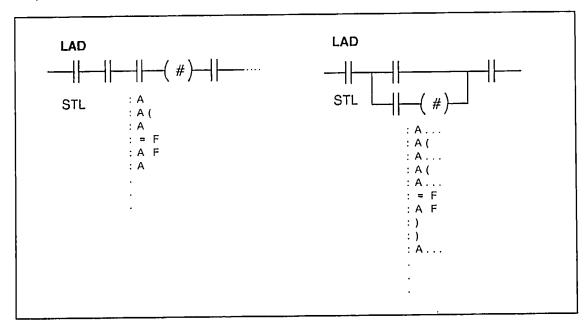

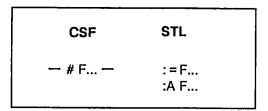

Depending on the programmer (PG) used a STEP 5 program may be written in the form of a control system flowchart (CSF), ladder diagram (LAD) or statement list (STL) (Fig. 1), thus enabling the programming method to be adapted to the application. The machine code (MC5) generated by the programmers is identical for all three. Depending on the programmer (PG) used, the user program can be translated from one method of representation to another by conforming to certain programming conventions (cf. Section 10).

| Ladder diagram                                                                      | Statement list                                         | Control system flowchart                                                        |

|-------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------|

| Programming with<br>symbols similar to<br>those used in sche-<br>matic circuit dia- | Programming with using mnemonics designating functions | Programming<br>with graphic<br>symbols                                          |

| grams<br>Complies with<br>DIN 19239<br>(draft)                                      | Complies with<br>DIN 19239<br>(draft)                  | Complies with<br>IEC 117 - 15<br>DIN 40700<br>DIN 40719<br>DIN 19239<br>(draft) |

| LAD                                                                                 | STL<br>A I<br>AN I                                     | CSF &                                                                           |

| -3EM-3E()<br>-3E                                                                    | A I<br>ON I<br>O I<br>= Q                              |                                                                                 |

Fig. 1.1 Methods of representing the STEP 5 programming language

## 1.3 Programming

## 1.3.1 Program structure

The PLC software comprises the operating system, the basic software and the user program. The operating system contains all statements and declarations for internal system functions. The basic software has a flexible interface to the operating basic functions (e. g. generation of data blocks, NC-PLC interface initialization, signal interchange with I/O modules). The basic software also contains pretested function blocks written in STEP 5 and assembled to form function macros.

The operating system and the basic software are integral components of the PLC; they are supplied on EPROMs, and may not be modified in any way.

The user program is the total of all statements and declarations/data programmed by the user.

The PLC structure makes structured programming essential, i. e. the program must be divided into individual, self-contained sections called blocks. This method offers the following advantages:

- Easy, lucid programming, even of large programs

- Easy standardization of program sections

- Simple program organization

- Fast, easy modification

- Simple program testing

- Easy start-up

A number of block types, each of which is used for different tasks, is available for structuring the user program:

- Organization blocks (OBs)

The OBs serve as interface between operating system and user program.

- Program blocks (PBs)

The PBs are used to break the user program down into technologically oriented sections.

- Function blocks (FBs)

The FBs are used to program frequently recurring complex functions (such as individual controls, reporting, arithmetic and PID control functions).

- Sequence blocks (SBs)

SBs are special forms of program blocks used primarily for processing sequencers.

- Data blocks (DBs)

DBs are used for storing data or texts, and differ in both function and structure from all other block types.

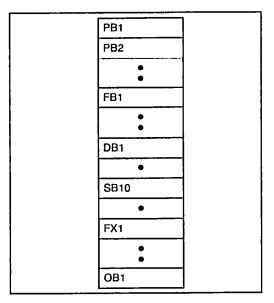

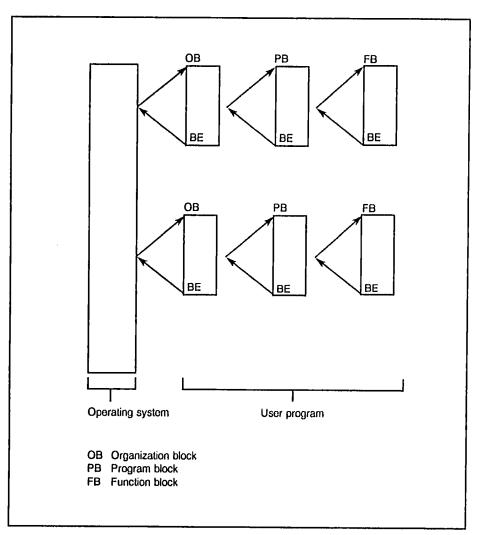

With the exception of the organization blocks, the maximum number of programmable blocks of each type is 255. The number of organization blocks may not exceed 64; of these, only OB 1, OB 2 and OB 20 are serviced by the operating system (cf. Section 5). The programmer stores all programmed blocks in arbitrary order in program memory (Fig. 1.2).

## 1.3.2 Program organization

The manner in which the program is organized determines whether and in what order the program, function and sequence blocks are executed. The order in which these blocks are involved is stipulated by programming the relevant calls (conditional or unconditional) in organization blocks (see Section 5.4, "Cyclic program").

Like the other blocks, the organization blocks are stored in user memory.

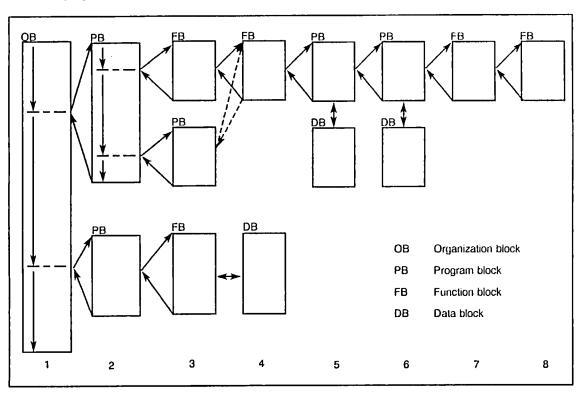

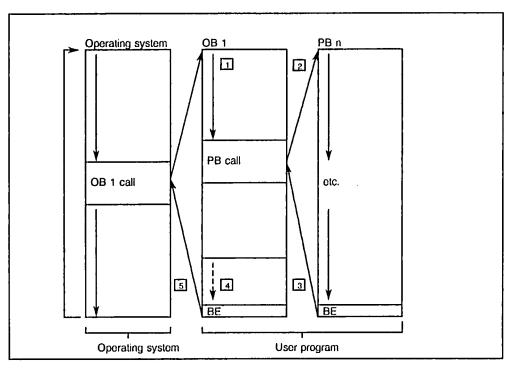

Different organization blocks are provided for various methods of program execution (cf. Section 5.2). Organization, program, function and sequence blocks can invoke other program, function and sequence blocks. The user program cannot call organization blocks. The maximum permissible nesting depth for organization blocks is 12 (Fig. 1.3), not including an accompanying data block, if any.

Fig. 1.2 Storing the blocks in arbitrary order in program memory

Fig. 1.3 Typical program organization in STEP 5 nesting depth 8 (maximum nesting depth = 12)

## 1.3.3 Program scanning methods

The user program can be scanned in three ways:

- One-shot scan in the controller's restart routine (following "Power up" or "RESET"). The statements to be executed must be programmed in OB 20.

- 2) Cyclic scanning of the statements in OB 1 based on an NC MD 155-dependent timing grid. When the default is in force, the operating system calls OB 1 every 66 ms; the following alternative time grids according to the times shows:

| MD 155   | Timing grid for OB1 |

|----------|---------------------|

| 0        | 60 ms               |

| <u>1</u> | <u>66 ms</u>        |

| 2        | 72 mS               |

| 3        | 78 ms               |

| 4        | 84 ms               |

| 5        | 90 ms               |

NC MD 155 permits only the standard value 1.

- 3) Event-driven, one-shot execution of the statements in OB 2, e. g. in response to an interrupt. Prerequisites for event-driven execution are as follows:

- Normal termination of the controller's restart routine

- Interrupt enable via PLC MD 2002, bit 0 = 0 (no interrupt service)

- A change in the interrupt input byte specified per MD (PLC MD 0)

Cyclic scanning can be interrupted by the high-priority NC functions' interrupt service routine or delayed pending termination of OB 2 following execution of each STEP 5 command.

## 1.3.4 Influencing factor: User program size

As mentioned in Section 1.1, execution of the STEP 5 program should not take up more then 15 % of the total available CPU time, nor should the interrupt service routine in OB 2 take up more time than necessary because of its high priority, as this would delay execution of important NC functions.

For this purpose, the execution times of both the cyclic user program and the interrupt service routine are monitored at the hardware level. The permissible runtimes can be set in PLC MD 1 (maximum interpreter time OB 1 + OB 2) to 3 (maximum interpreter time PLC-interrupt service), whereby confirmation of the defaults ensures that the "integrated PLC" will not take up more than the admissible amount of CPU time. When these values are exceeded, the PLC goes to the state specified in bit 0 or 1 of PLC MD 2003; when the defaults are used, the "integrated PLC" always enters the Stop mode.

When the user programs exceed the permissible execution times only slightly, program scanning can be upheld by modifying these machine data bits, but this may adversely affect the NC functions.

There are two ways of ensuring the executability of large cyclic user programs (max. 6K words) without placing an excessive load on the CPU:

- Fragmenting cyclic execution through autonomous interrupts

- Allowing cyclic execution to be interrupted by higher-priority program blocks only

The mode is set in PLC MD 2003, bit 6 (fragmenting of S5 program execution). The percentage in MD 1 thus assumes the following meaning as regards the scan time:

- No fragmenting (bit 6 of PLC MD 2003 = 0 = default):

15% of the cyclic program's timing grid (66 ms) results in a permissible runtime of 9.9 ms, when the default is used as basis.

- Fragmenting (bit 6 of PLC MD 2003 = 1)

Using the default as basis, 15% of 1/3 of the cyclic program's timing grid (66 ms) results in a runtime of 3.3 ms. The cyclic program then interrupts itself autonomously, and resumes execution in the next third.

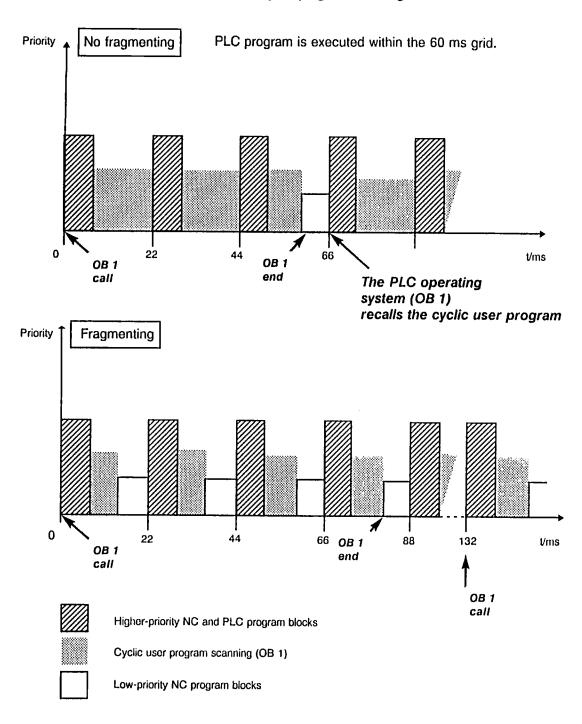

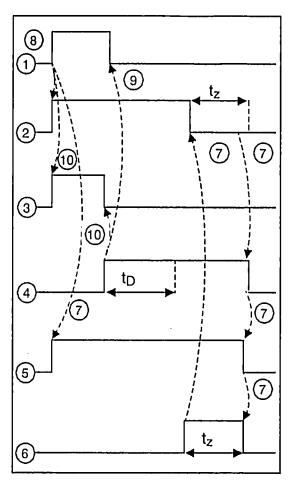

Graphic overview of the two methods for cyclic program scanning:

When the OB 1 (cyclical user program) is too large to be executed within a 66 ms grid, fragmenting must be selected.

As already mentioned, the timing grid, based on the default, is  $12 \cdot \text{scanning time } (12 \cdot 5.5 \, \text{ms})$ . The admissible execution time of the cyclic program for both variants can also be increased by augmenting PLC MD 1 (CPU load in %).

The admissible runtime for the interrupt service routine (PLC MD 3), regardless of the cyclic execution mode, may not exceed 2000  $\mu$ s (standard value) in an interval of 4 · scanning time (4 · 5.5 ms = 22 ms).

The entire runtime may either be used for one-shot execution of the statements in OB 2 or, in an extreme situation, for 4-shot execution of OB 2, as the interrupt input byte is scanned for an edge change on the basis of the scanning time. If the default runtime for OB 2 proves insufficient, PLC MD 3 (maximum interpreter time PLC-interrupt service) must either be incremented (to max. 2500  $\mu$ s) or the PLC set to the Stop mode when OB 2 exceeds the allotted time by modifying bit 1 in MD 2003. The example on the next page emphasizes the difference between the two variants for a cyclic user program with a runtime time of 25 ms.

#### No fragmentation:

The cyclic user program may be interrupted by higher-priority NC and PLC program blocks only (e. g. position control, interpolation, monitoring functions, programming and test functions, interrupt service routine (OB 2)). It is otherwise continued until it has terminated and all signals it generated have been forwarded to their destinations (NC, I/Os). Only then can the low-priority functions execute.

Depending on the size of the STEP 5 program in OB 1, the remaining interval may be quite short, as the operating system recalls the cyclic program when 66 ms have passed. The consequence is that too little time is available for the low-priority functions, a fact which becomes immediately apparent in a sluggish "operator interface". Display construction is extremely slow, as is the controller's reaction to keyboard entries. In extreme situations, the low-priority functions are allotted almost no time at all to execute.

In the example, the CPU load caused by the STEP 5 program alone would escalate to value x, where

$$x = \frac{25 \text{ ms}}{66 \text{ ms}} \cdot 100 \% = 37 \%$$

, assuming that cyclic execution

is terminated within 66 ms. If this is not the case, execution will terminate in the next interval and be restarted immediately if no higher-priority functions are pending. In the example, no regard was paid to the 5% basic load resulting from data transfers prior to and following the OB 1 call.

It is obvious that a CPU load of almost 42% for the controller alone is not acceptable.

#### **Fragmenting**

When this variant is used, the cyclic program interrupts itself autonomously. If the default is used, the CPU load, refered to the cyclic program timing grid, would be:

$$x = \frac{3.3 \text{ ms} \cdot 3}{66 \text{ ms}} \cdot 100 \% = 15 \%$$

The basic load for the cyclic program, about 5%, must be added to this, so that the cyclic program load on the CPU would always be ≤ 20 %. It is less than 20% when cyclic execution is not terminated within one timing period. Extremely long cyclic user programs may cause the cycle time monitor to response (defaulöt: 300 ms).

By selecting the diagnostics function (MD 2003, bit 7 = 1), the user can obtain a general view of the anticipated run time for STEP 5 programs as well as the required cycle time. On the basis of these data, he can optimize the configuration of his MD as regards his job requests and the purpose for which the controller is to be used.

#### Options for initiating the diagnostics function:

1) One-time-only display via the "STATUS VARIABLE" programmer function

| DB 1 DW 0 KF = <current cycle="" in="" ms="" time=""> DW 1 KF = <interpreter 1="" 2="" and="" in="" ob="" runtime="" µs=""> DW 2 KF = <cyclic in="" interpreter="" runtime="" µs=""> * DW 3 KF = <interrupt-driven in="" interpreter="" runtime="" µs=""> * DW 4 KF = <number interrupts="" of="" serviced=""> * DW 9 KH = 8000</number></interrupt-driven></cyclic></interpreter></current> | STATUS | VARIABLE                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------|

| DW 1 KF = <interpreter 1="" 2="" <math="" and="" in="" ob="" runtime="">\mus &gt; DW 2 KF = <cyclic <math="" in="" interpreter="" runtime="">\mus &gt; * DW 3 KF = <interrupt-driven <math="" in="" interpreter="" runtime="">\mus &gt; * DW 4 KF = <number interrupts="" of="" serviced=""> *</number></interrupt-driven></cyclic></interpreter>                                            | DB 1   |                                                                                    |

| DW 2 KF = <cyclic in="" interpreter="" runtime="" µs=""> * DW 3 KF = <interrupt-driven in="" interpreter="" runtime="" µs=""> * DW 4 KF = <number interrupts="" of="" serviced=""> *</number></interrupt-driven></cyclic>                                                                                                                                                                    | DW 0   | KF = <current cycle="" in="" ms="" time=""></current>                              |

| DW 3 KF = <interrupt-driven in="" interpreter="" runtime="" µs=""> * DW 4 KF = <number interrupts="" of="" serviced=""> *</number></interrupt-driven>                                                                                                                                                                                                                                        | DW 1   | KF = <interpreter 1="" 2="" and="" in="" ob="" runtime="" μs=""> *</interpreter>   |

| DW 4 KF = < number of interrupts serviced > *                                                                                                                                                                                                                                                                                                                                                | DW 2   | KF = <cyclic in="" interpreter="" runtime="" μs=""> *</cyclic>                     |

| <u>,                                      </u>                                                                                                                                                                                                                                                                                                                                               | DW 3   | KF = <interrupt-driven in="" interpreter="" runtime="" μs=""> *</interrupt-driven> |

| DW 9 KH = 8000                                                                                                                                                                                                                                                                                                                                                                               | DW 4   | KF = < number of interrupts serviced > *                                           |

|                                                                                                                                                                                                                                                                                                                                                                                              | DW 9   | KH = 8000                                                                          |

Note:

The initiate bit in DW 9 is set once via the programmer, and is reset by the PLC operating system at the start of the cycle when the current values are transferred to DB 1.

#### \* Values relate to the current scan time

2) Periodic display via the "STATUS" programmer function and a corresponding initiation routine in OB 1.

OB<sub>1</sub>

Note:

This enables a fairly accurate estimation of the fluctuations in the runtimes (cycle time and interpreter runtime are not constant values!), and is the only way to show the interrupt-driven interpreter runtime (OB 2) and the number of interrupts serviced (e. g. by simulating a change in the interrupt input byte at the hardware level).

Representation of the number format must be changed from KF to KH when the interpreter runtime exceeds 32768 µs, as the display would otherwise be incorrect.

## 2 Program blocks

## 2.1 Programming program blocks

The information presented in this Section applies to the programming of organization, program and sequence blocks. These three block types are all programmed in the same way. Section 3 gives information on programming data blocks and section 4 information on programming function blocks. Program, organization and sequence blocks can be programmed in all three STEP 5 modes of representation using the basic operations.

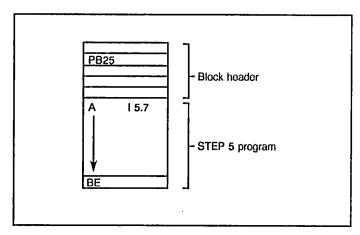

The first step in programming a program block (PB) is the specification of a program block number between 0 and 255 (example: PB 25). This is followed by the actual control program, which is terminated with a "BE" statement.

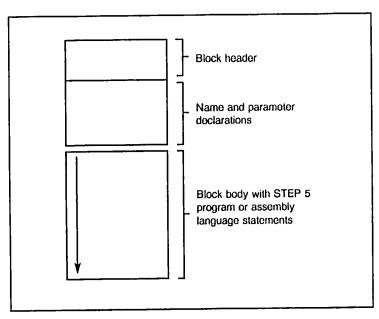

An S5 block comprises two parts:

- Block header

- S5 operations (block body)

The block header, which the programmer generates automatically, takes up five words in program memory.

A program block should always be a self-contained program. Logical links to other blocks serve no practical purpose.

Fig. 2.1 Structure of a program block

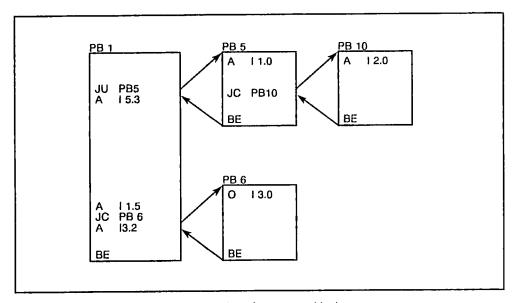

## 2.2 Calling program blocks

Block calls are used to release the blocks for execution (Fig. 2.2). These block calls can be programmed only in organization, sequence, program or function blocks. (Only organization blocks may not be invoked by the user program). A block call is comparable to a "subroutine branch", and may be both conditional and unconditional.

A "BE" statement is used to return to the block that contained the block call. No further logic operations can be carried out on the RLO following a block call or a "BE". The RLO (result of the logic operation) is passed to the "new block", and can be evaluated there.

#### Unconditional call: JU xx

The program block is executed without regard to the RLO.

#### Conditional call: JC xx

The program block is executed in dependence on the RLO.

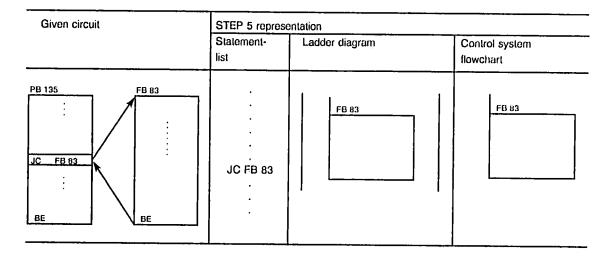

Fig. 2.2 Block calls for enabling execution of a program block

## 3 Data blocks

### 3.1 Programming Data Blocks

The data required by the user program is stored in data blocks (DBs). No STEP 5 operations are programmed in these blocks.

#### Data may be:

Arbitrary bit patterns, e. g. for plant status indications

Numbers (hexadecimal, binary, decimal), e. g. for times and results of arithmetic operations Alphanumeric characters, e. g. for message texts

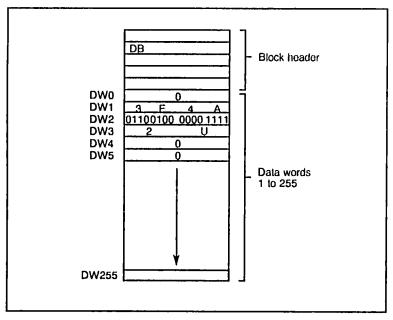

Generation of a data block on the programmer begins by specifying a data block number between 1 and 255. Each data block (example: DB99) may comprises as many as 256 data words (of 16 bits each) (Fig. 3.1). The data must be entered by word, beginning with data word 0.

One word is reserved in program memory for each data word. The programmer also generates a block header for each data block; the header takes up five words in program memory.

The operating system generates data blocks DB 1 (diagnostics DB), DB 36 (read/write job status for NC data) and DB 37 (initialize the two V.24 (RS232C) interfaces) in the controller's restart routine. The programmer (PG) prevents deletion of these blocks (message 70: DB in EPROM).

For test purposes, however, the user can invoke the "Force Variable" programmer function if he wants to view or modify data words.

Fig. 3.1 Structure of a data block

## 3.2 Calling data blocks

Data blocks can be called unconditionally only. Once called, a data block remains in force until the next is invoked.

User data blocks must not conflict with those required by the system.

A data block call can be programmed in an organization, program, function or sequence block. The "C DB xx" command calls a data block.

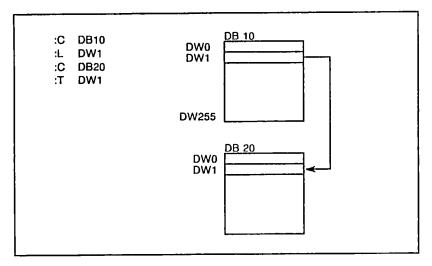

#### Example 1

Transferring the contents of data word 1, data block 10 to data word 1, data block 20 (Fig. 3.2).

Fig. 3.2 Calling a data block

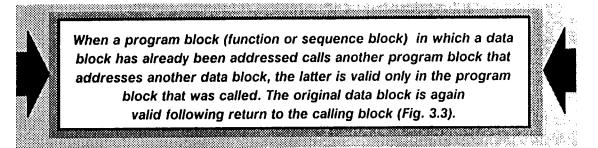

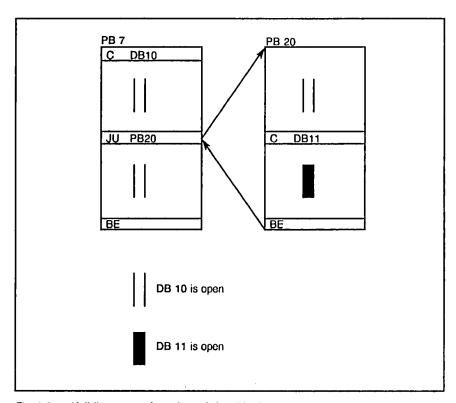

#### Example 2

Data block 10 is called in program block 7, and the data in this data block are subsequently processed.

Program block 20 is then called and executed. Data block 10 is still valid. Only when data block 11 has been selected or opened is the data area changed.

Data block 11 is now valid until program block 20 has terminated.

Data block 10 is once again valid following the return to program block 7.

Fig. 3.3 Validity range of a selected data block

## 4 Function Blocks

#### 4.1 General Remarks

Function blocks are used to implement frequently recurring or extremely complex functions.

Functions blocks (FBs) are as much a part of the user program as, for example, program blocks. There are three basic differences between function blocks and organization, program or sequence blocks:

- Function block can be initialized, i. e. a function block's formal parameters can be replaced by the actual operands with which the function block is called.

- In contrast to organization, program and sequence blocks, an extended operation set comprising the STEP 5 supplementary operations (see also Section 9.4) can be used to program function blocks, and only function blocks.

- The program in a function block can be generated and logged in statement list form only.

The function blocks in a user program represent complex, self-contained functions. A function block programmed in the STEP 5 language can be programmed by the user himself, or may be purchased from Siemens as a software product. In addition, a number of pretested, technology-specific function blocks can be assembled to form function macros and linked into the basic program. The user can call these macros as he would a function block, but he cannot modify them. These blocks are written in assembly language and are also referred to as "resident" or integral function blocks" (cf. Section 6.1).

## 4.2 Structure of Function Blocks

A function block comprises a block header, name and parameter declaration, and the block body (Fig. 4.1).

Fig. 4.1 Structure of a function block

## 4.2.1 Block header

The block header contains all information which the programmer needs in order to display the function block in graphic form and check the operands when the function block is initialized. The user must enter the header (using the programmer) before programming the function block.

#### 4.2.2 Block body

The block body contains the actual program, i. e. describes the function to be executed in the STEP 5 language. Only the block body is processed when the function block is called.

The programmer echoes the block name and parameter declaration when integral assembly-language function blocks are called.

When the "first executable statement" in the block body is the "ASM" STEP 5 command (switch to assembly code), the processor executes the subsequent assembly language statements immediately.

## 4.3 Calling and Initializing Function Blocks

Function blocks (FBs) are present only once in memory. They can be called once or more than once by a block, and different parameters can be used for each call.

Function blocks are programmed or called by specifying a block number (FB 0 to 255).

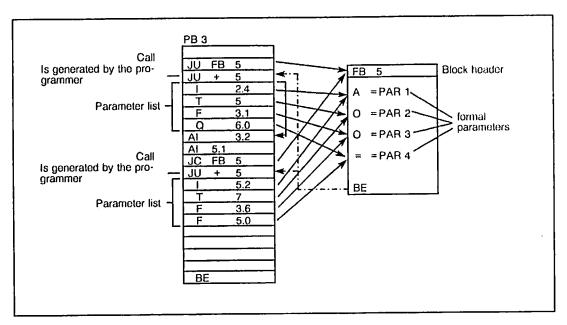

A function block call can be programmed in an organization, sequence or program block or in another function block. A call comprises the call statement and the parameter list.

#### 4.3.1 Call statement

JU FB n Unconditional call JC FB n Conditional call

#### **Unconditional call:**

The function block is executed without regard to the RLO.

#### Conditional call:

The function block is executed only when the RLO = 1.

#### 4.3.2 Parameter list

The parameter list immediately follows the call statement (Fig. 4.2), and defines all input variables, output variables and data. The parameter list may contain no more than 40 variables.

The variables from the parameter list replace the formal parameters when the function block is executed. The programmer (PG) monitors the order in which the variables are entered in the parameter list.

The programmer automatically generates, but does not display, the jump statement that follows the FB call.

The FB call reserves two words in program memory, and each parameter one additional word.

The identifiers for the function block's inputs and outputs and the name of the function block are displayed on the programmer when the user programs the function block. This information is in the function block itself. It is therefore necessary that all required function blocks either be resident as function macro in the PLC's basic software, be transferred to the program diskette, or be entered directly into the programmable controller's program memory before function block programming can begin (for details, refer to the Operating Instructions).

Fig. 4.2 Calling a function block

## 4.4 Programming function blocks

In keeping with its structure, a function block is generated in two parts: the block header and the block body.

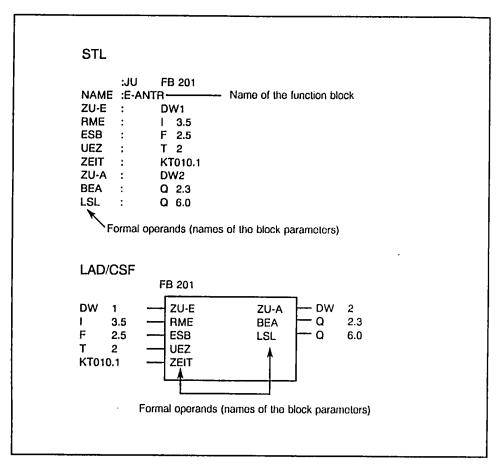

The block header must be entered before the block body (STEP 5 program). The block header contains:

- The library number

- The name of the function block

- The formal operands (the names of the block parameters)

- The block parameters

## 4.4.1 Library number

The library number may be a number between 0 and 65535. The function block is assigned this number without regard to its symbolic or absolute parameters.

A library number should be assigned only once to permit unique identification of a function block. Standard function blocks have a product number.

#### 4.4.2 Name of the function block

The name that identifies the function block may comprise no more than eight characters, the first of which must be a letter.

## 4.4.3 Formal operand (block parameter name)

A formal operand may comprise no more than four characters, the first of which must be a letter. A maximum of 40 parameters can be programmed per function block.

Fig. 4.3 Sample function block call

## 4.4.4 Block parameter types

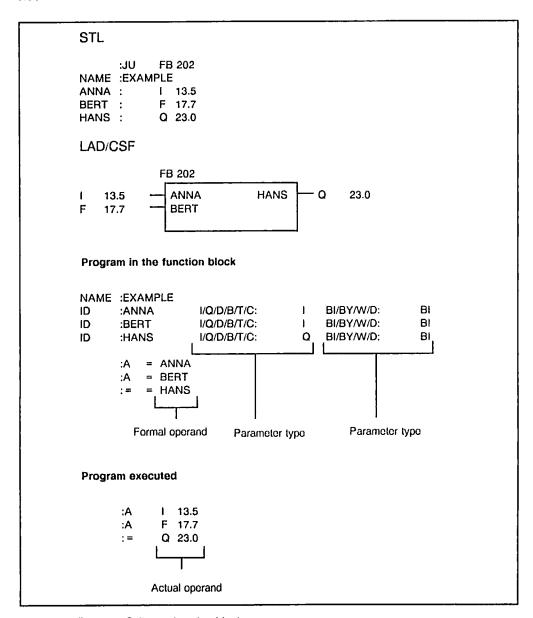

A block parameter may be of type "I", "Q", "D", "B", "T", or "C".

I = Input parameter

Q = Output parameter

D = Data

B = Block

T = Timer

C = Counter

In graphic representation, parameters of type "I", "D", "B" and "C" are shown at the left of the function symbol and those of type "Q" at the right. Operations to which parameters are to be assigned (substitution operations) are programmed in the function block with formal operands. The formal operands may be addressed at various locations within the function block.

Fig. 4.4 Example: Calling a function block

## 5 Organization Blocks

## 5.1 General Remarks

The organization blocks form the interface between the operating system and the user program.

The organization blocks (OBs) are as much a part of the user program as are program blocks, sequence blocks and function blocks, but only the operating system can invoke them. A user can only program organization blocks; he cannot invoke them (Fig. 5.1).

Fig. 5.1 PLC program

Appropriate programming of the organization blocks enables the following:

- One-shot execution following PLC restart (OB20)

- Cyclic execution (OB 1) (see "Programming the cyclic program")

- Execution of the interrupt service routine (OB 2) (see "Programming the interrupt service routine")

OB 2 must be available when interrupt processing is enabled (MD 2002, bit 0 = 0), otherwise the PLC will stop. OB 20 and OB 1 can be installed in the PLC as required. If one of these two OBs is missing this fact is ignored by the operating system.

The organization blocks are programmed in the same manner as program or sequence blocks, and can be programmed and documented in all three methods of representation (statement list STL, control system flowchart CSF, ladder diagram LAD).

## 5.2 Cyclic scanning

#### 5.2.1 Interrupt capability

The cyclic user program can be interrupted after each MC 5 instruction. The last instruction is executed in its entirety and pending interrupts (caused by a process interrupt or higher-priority sections of the NC program) are enabled when the instruction been executed.

If the interrupt was caused by detection of an edge change in the interrupt input byte, all MC5 registers, as well as flag bytes 224 to 255, are saved; these registers and flag bytes are recovered following termination of the interrupt service routine. The data block open prior to the interrupt is thus once again valid.

## 5.2.2 Response time and scan time

#### a) Response time:

The response time to a process signal or a signal from the NC is defined as follows: The PLC operating system forwards the signal to the user interface (I, F area), invokes and executes the cyclic user program (OB 1) and transfer the process output image updated by OB 1 to the I/Os and the NC.

The response depends on:

- 1) Type and length of the cyclic user program in OB 1

- 2) Execution mode of the cyclic user program (MD 2003, bit 6: fragmentation, no fragmentation)

- 3) Timing grid for the cyclic user program (MD 155: scanning time)

- 4) Execution time of the higher-priority NC program blocks and of the interrupt service routine (OB 2) where applicable

- 5) Instant: Process image updating by the PLC operating system and actual signal status change (I/Os, internal NC-PLC interface)

#### b) Cycle time:

The cycle time is the period between two updatings of the process input image by the PLC operating system. Because the PLC invokes the cyclic user program in accordance with a specific timing grid (NC MD 155-dependent) rather than restarting it immediately after it has terminated, the cycle time can never be less than 60 ms (default: 66 ms).

Like the response time, the cycle time is dependent on the conditions listed in 1-4 (above). It can be ascertained by invoking the diagnostic function (MD 2003, bit 7 = 1), and is monitored to ensure that it does not exceed a maximum value (PLC MD5 default is 300 ms). If it does, the PLC will stop.

#### 5.2.3 Programming the cyclic program

A programmable controller's program is "normally" scanned cyclically (Fig. 5.4). The processor starts at the beginning of the STEP 5 program, scans the STEP 5 statements sequentially until it reaches the end of the program, and then repeats the entire procedure.

## 5.2.4 Interface between operating system and cyclic program

Organization block OB 1 is the interface between the operating system and the cyclic user program. The first STEP 5 statement in OB 1 is also the first statement in the user program, i. e. is equivalent to the beginning of the cyclic program.

The program, sequence and function blocks comprising the cyclic program are called in organization block 1. These blocks may themselves contain block calls, i. e. the blocks can be nested (see Section 1, "Program organization").

Fig. 5.4 Cyclic program scanning

- First statement in the STEP 5 program.

- First PB call. The block called may contain additional calls (cf. Section 1, "Program organization").

- Return from the last program or function block executed.

- 4 The organization block is terminated with BE.

- E Return to operating system.

The user program's runtime is the sum of the runtimes of all blocks called. When a block is called "n" times, its runtime must be added to the total "n" times.

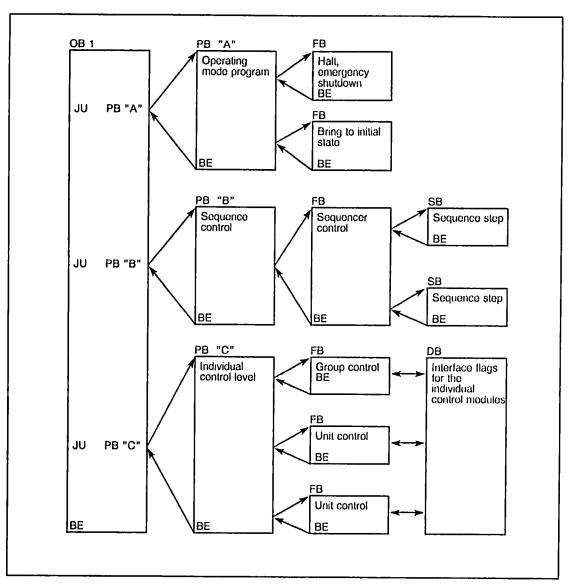

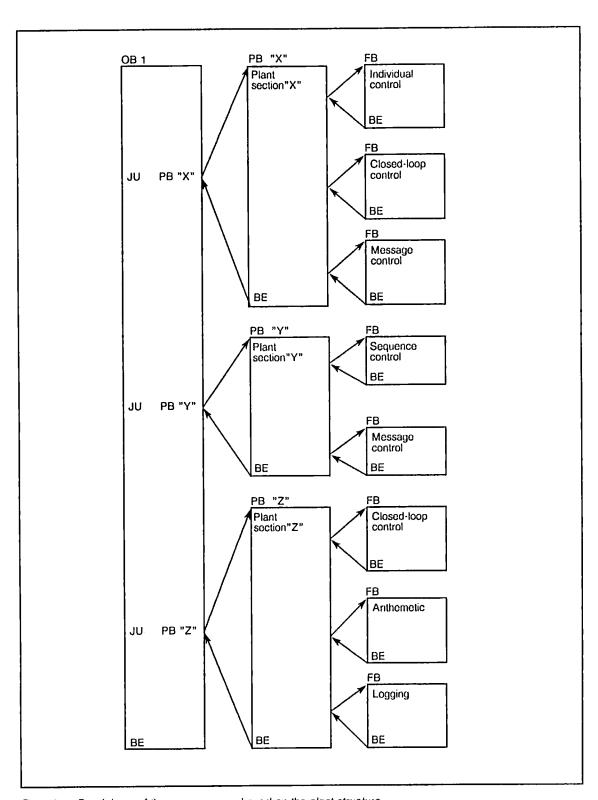

## 5.2.5 Basic program organization

Organization block OB 1 contains the basic structure of the user program. A diagram of this block shows the essential program structures at a glance (Fig. 5.5) and emphasizes program-interdependent plant sections (Fig. 5.6).

Fig. 5.5 Breakdown of the user program based on the progam structure

Fig. 5.6 Breakdown of the user program based on the plant structure

# 5.3 Interrupt Processing

# 5.3.1 Programming the interrupt service routine

The PLC has interrupt-processing capabilities.

In this mode, the cyclic program is interrupted and an interrupt service routine (OB 2) executed. Once the interrupt service routine has terminated, the processor returns to the point of interruption and resumes execution of the cyclic program.

The interrupt service routine is initiated when the signal state of specific input bits changes (edge-triggered).

Interrupt service routines allow the user to react immediately to process signals. An edge change in these signals is thus registered before the process image is updated, thereby minimizing the response time to time-critical functions in the process.

Because the PLC operating system does not transfer the process image to the I/Os when OB 2 terminates, the user must himself influence the process peripherals with STEP 5 commands T PB/T PW.

Over the interrupt service routine, signals can be forwarded at high speed to the NC in output bytes QB 90 (program override channel 1) and QB 99 (program override channel 2); the NC then transfers these signals in a 22 msgrid (in dependence on NC-MD 155) to the internal NC PLC interface.

Note: No further processing takes place on the NC end up to this point.

# 5.3.2 Interface between operating system and the interrupt

OB 2 is the interface between the operating system and the interrupt service routines.

OB 2 is always invoked when the signal state of a bit in the interrupt input byte changes.

The user may select the input bit and it via machine data (PLC MD 0: maximum value 31). MD 2002, bit 0 must also be set to 0 to enable interrupts.

When one of the selected bits changes from "0" to "1" (positive edge) or from "1" to "0" (negative edge), the interrupt service routine is invoked, i. e. the operating system calls OB 2, which contains the user's interrupt service routine.

The operating system checks the interrupt bytes every 5.5 ms (in dependence on MD 155), and invokes an interrupt service routine when required.

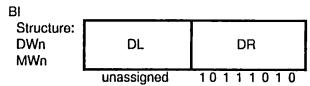

The type of signal change (positive or negative edge) is entered as input parameter in flag bytes FB 12 and FB 16.

The PLC operating system resets flag bytes FB 12 and FB 16 when OB 2 terminates.

# 5.3.3 Response time

The following factors influence the interrupt service routine's response time to an edge change in the interrupt input byte:

- 1. Whether the interrupt input byte is a global or local I/O byte

- 2. The sampling time (NC MD 155)

- 3. The instant at which the edge change takes place in the interrupt input byte and that at which the PLC operating system scans that byte

Approximate response times:

Global interrupt input byte:

The response time is between 2 ms and 7.5 ms.

Local interrupt input byte:

The response time is between 3.5 ms and 9 ms.

# 6 Integral Function Blocks

## 6.1 General Remarks

Function macros are function blocks that are written in assembly language and integrated in the operating system.

The user can invoke and initialize these blocks in the same way as STEP 5 blocks. They are used for time-critical functions, and execute much faster than comparable STEP 5 blocks. The user should therefore give the integral blocks preference over the conventional STEP 5 blocks.

Note the following when linking the blocks into the user program:

- 1. These blocks can be called by other blocks when the user program is generated ON-LINE (entered direct in the PLC from the programmer). The corresponding parameter table is displayed on the PG screen, and the user can make all required entries.

- 2. When programming direct on diskette, the function macros to be called must be disk-resident, i. e. the user must transfer the macros from the PLC to a workdisk. Only the block headers with parameter block are transferred.

When these FBs are called in the user program, the user need only initialize the parameter table. The block headers must not be transferred when the user program is transferred to EPROM.

### Loading the PLC blocks:

STEP 5 function blocks that have the same numbers as function macros cannot be transferred to the PLC (PG message: "Block already in EPROM").

# 6.2 FB Identifiers

| FB call                 | Parameter type                | Data type                                                                              | Permissible actual operands                                                                                                                                                           |

|-------------------------|-------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FB Name                 | I Input<br>Q Output           | BI Operand with bit address                                                            | I n.m Input<br>Q n.m Output<br>F n.m Flag                                                                                                                                             |

| §1,                     |                               | BY Operand with byte address  W Operand with word address                              | IB n Input byte  QB n Output byte  FB n Flag byte  DL n Data byte left  DR n Data byte right  PB n Peripheral byte  IW n Input word  QW n Output word  FW n Flag word  DW n Data word |

| T — C — \$F             | B Block                       | Not applicable                                                                         | PW n Peripheral word  DB n Data block FB n Function block PB n Program block SB n Sequence block                                                                                      |

| \$DW   \$DW             | T Timer                       | Not applicable                                                                         | T n No. of the timer                                                                                                                                                                  |

| *F *F                   | C Counter                     | Not applicable                                                                         | Z n No. of the counter                                                                                                                                                                |

| *DW *DW *DW *N 1 - *% 1 | D Data                        | KH Hexadecimal nur<br>KS Two alphanumer<br>KT Time (1.0 to 999)<br>KC Count (0 to 999) | ulues (1 per byte) from 0 to 255<br>mber, max. 4 digits<br>ric characters<br>9.3)                                                                                                     |

|                         | I,BI -Q<br>I,BI -/            | Static input signal<br>Input signal acknowledg<br>Input signal whose risin             |                                                                                                                                                                                       |

|                         | §1, —<br>\$ —                 |                                                                                        | ameter<br>t be supplied prior to calling the FB<br>n need not be generated                                                                                                            |

|                         | Q- Q,BI<br>Q- Q,BI<br>I- Q,BI | Output signal for one cy                                                               | I flag word or data word which can                                                                                                                                                    |

|                         |                               | error code                                                                             | o. g. NC signal system stop (STS); ACCU 1 nterface byte in ACCU2's HIGH                                                                                                               |

# 6.3 Function macros

| FB no. | FB ID       | FB NAME                          | Pago        |

|--------|-------------|----------------------------------|-------------|

| 11     | EINR-DB     | Generate data blocks             |             |

| 60     | FB BLOCK-TR | Block transfer                   |             |

| 61     | FB NCD-LESE | Road NC data                     |             |

| 62     | FB NCD-SCHR | Write NC data                    |             |

| ,      |             |                                  |             |

| ,      |             |                                  |             |

| 65     | M→STACK     | Transfer flags → flag stack      |             |

| 66     | STACK→M     | Flag stack → transfer flags      | †           |

| ,      |             |                                  |             |

| •      |             |                                  |             |

| 80     |             |                                  |             |

| 81     |             |                                  |             |

| 82     |             |                                  |             |

| 83     |             |                                  |             |

| 84     |             |                                  |             |

| 85     |             |                                  |             |

| 86     |             |                                  |             |

| 87     |             |                                  |             |

| 88     |             |                                  |             |

| ı      |             |                                  |             |

| ,      |             |                                  |             |

| 1      |             |                                  | <del></del> |

| 190    | K-LEITPC    | Data interchange with master PLC |             |

|        |             | J                                |             |

# FB 11 EINR-DB Generate data blocks

### 1. Description

The EINR-DB function block is used to generate data blocks for variable data in the PLC's RAM.

EINR-DB generates the specified data block, e.g. in the cold restart routine (OB 20), but only when the DB is not yet in the address table and a valid data word number (DWNR < 255) is specified.

The interface flags (FW 246 and FW 248) are evaluated when parameter AN = 0.

- 255 < DW number < 0</li>

- Data block number > 255

- Data block number = 0

- Not enough RAM available in PLC

- Data block already in PLC and lengths are not identical

A detailed error identifier is entered in ACCU 2 (ACCU 1 contains the block number). The data block is initialized to zero.

Note: The data blocks for the basic software (interface data blocks) are generated

automatically in the cold restart routine.

### 2. Block data

Lib.-No. :

FBs to be loaded : None DBs to be loaded : None

Type of FB call : unconditional or conditional (JU FB11 or JC DB11)

DBs to be entered : None

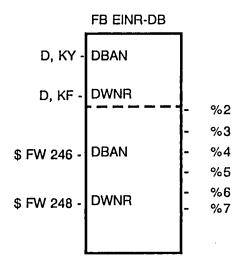

Error messages : %2 DB no. > 255

%3 Spec. DWNR < 0

%4 Length of DBto be generated not identical with length of DB in PLC

%5 Not enough RAM available in PLC

%6 Spec. DWNR > 255 %7 DB0 cannot be generated

### 3. Block call

## 4. Signals

**DBAN** Number of data blocks to be generated and their numbers.

### Special case:

When parameter AN is 0, the function block can be initialized over flag words FW 246 and FW 248.

High-Byte: DB number

Low-Byte: Number of data blocks (minimum of 1)

**DWNR** No. of the last DW

### 5. Example

Data blocks 150 and 151 are generated from data word 0 to data word 250.

### FB 60 BLOCK-TR Block transfer

### 1. Description

Function block BLOCK-TR transfers the specified number of data words from a source DB located in RAM or EPROM to a destination DB in RAM.

The user may specify both the start of the source DB block to be transferred and the start data word in the destination DB.

Prior to initiating the transfer, the PLC checks to make sure that:

- the source DB in the PLC has the required length

- the destination DB in the PLC has the required length

- the destination DB is located in RAM

- the number of data words to be transferred is > 0 and < 128.</li>

The PLC enters the Stop loop when an error is detected. A detailed error identifier is entered in ACCU 2 (ACCU 1 = block number). Flag words FW 250-254 are scanned when the "DB QZ" parameter is zero.

### 2. Block data

(Initialization: 0,1 1,0 or 0,0).

Lib. no.

•

FBs to be loaded

: None

DBs to be loaded

: None

Type of FB call

: Absolute or conditional (JU FB 60 or JC FB 60)

DBs to be entered

: None

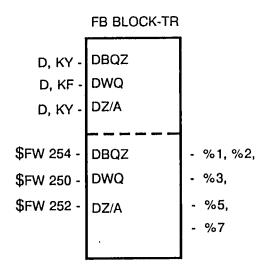

Error messages

: %1 No. of DWs to be transferred > 127

%2 No. of DWs to be transferred = 0

%3 No source DB

%4 No destination DB

%5 Destination DB too short

%6 Destination DB is in EPROM

%7 Source DB too short

### 3. Block call

## 4. Signals

DBQZ Source DB and destination DB numbers

High-Byte : Source DB Low-Byte : Destination DB

DWQ Start of the data block to be copied in the source DB

DZ/A Start of the data block in the destination DB and number of data words to be

transferred

High-Byte : Start of the data block

Low-Byte : Number of data words to be transferred

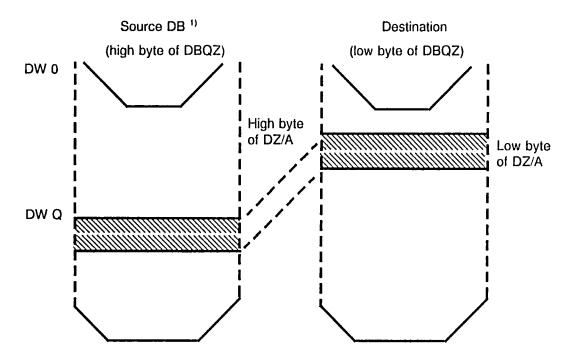

### 5. Example

FB BLOCK-TR

10,11 -- DBQZ 8 -- DWQ 12,05 -- DZ/A

5 data words, beginning with DW 8, are copied from DB 10 to DB 11; the first destination data word is DW 12.

### 6. Data transfer diagram

<sup>1)</sup> The "source" data block may be located in either RAM or EPROM

# FB 61 NCD-LESE Read NC data FB 62 NCD-SCHR Write NC data

### Description

Function blocks FB 61 and FB 62 are used to read NC data from/write NC data to the PLC. Prerequisite is that the job-controlled data interchange between NC and PLC has been enabled by an option bit (error 8 is output when this is not the case).

Parameters must be initialized to inform the function blocks of the data source in the NC or PLC and of the data destination in the PLC or NC. The function blocks must be assigned a byte in the interface data area (DB 36) over the NBSY parameter; this byte informs the function blocks of the current state of the data transfer.

The NC/PLC data transfer function is described in detail in Section 7. NC interrupt 3016 is issued when the NC's data type is unknown.

### 2. Block data

Lib. no. FB61

FB62

FBs to be loaded : None DBs to be loaded : None

Type of FB call : Unconditional or conditional

DBs to be entered

: None

Error messages

: ACCU 1 (FB no.) = 61 or 62

ACCU 2, high byte, = No. of the interface byte, i. e. the number of

the job that produced the error (exception: error 8).

ACCU 2 low byte = detailed error code:

0 : ANZ >1 not allowed1 : Invalid interface byte

2 : Addressed data word missing / DB missing or DB no. / FW no. invalid

3 : Invalid data type4 : \*ANZ = < 0 or >80

5 : Illegal read / illegal write

6: Invalid number format

7: Value 3 (WER3) not 0 (ZOA) or 1 (ZOFA)8: Read /write NC data not enabled by option bit

<sup>\*</sup> Refer to the exceptions for the ANZ parameter

### 3. Block call

FB 61: NCD-LESE

|                                                                                  | _ |                                                       | _            |                                                      |

|----------------------------------------------------------------------------------|---|-------------------------------------------------------|--------------|------------------------------------------------------|

| I, BI I, BY D, KF D, KS D, KS D, KF D, KF D, KF D, KF                            |   | LESE NSBY ANZ DTY1 DTY2 DTY3 WER1 WER2 WER3 ZFPN ZIEL |              |                                                      |

| \$FB 242<br>\$FB 243<br>\$FW 244<br>\$FW 248<br>\$FW 250<br>\$FW 252<br>\$FW 254 |   | NSBY<br>ANZ<br>WER1<br>WER2<br>WER3<br>ZFPN<br>ZIEL   | <br><br><br> | % 0<br>% 1<br>% 2<br>% 3<br>% 4<br>% 5<br>% 6<br>% 7 |

|                                                                                  | L |                                                       | i            |                                                      |

FB 62: NCD-SCHR

|                                                                                  |                                                                                     | _ |                                                             |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---|-------------------------------------------------------------|

| I, BI I, BY D, KF D, KS D, KS D, KF D, KF D, KF                                  | SCHR<br>NSBY<br>ANZ<br>DTY1<br>DTY2<br>DTY3<br>WER1<br>WER2<br>WER3<br>ZFPN<br>QUEL |   |                                                             |

| \$FB 242<br>\$FB 243<br>\$FW 244<br>\$FW 248<br>\$FW 250<br>\$FW 252<br>\$FW 254 | <br>NSBY<br>ANZ<br>WER1<br>WER2<br>WER3<br>ZFPN<br>QUEL                             |   | % 0<br>% 1<br>% 2<br>% 3<br>% 4<br>% 5<br>% 6<br>% 7<br>% 8 |

# 4. Signals

LESE Command for data transfer

SCHR The parameters are transferred to the FIFO buffer (job buffer) when the LESE (read) or SCHR (write) signal = 1.

In case of an unconditional block call, the user has to reset the LESE or SCHR signal at the end of the data transfer.

On an unconditional block call, the signal must be set to "1" (F 0.1) (see also timing diagrams). Data transfer can be activated only when the initialized interface byte's (NSBY's) DATA TRANSFER ENABLED signal is 0.

NSBY The function block must be assigned a byte in the interface data area (DB 36) from which it can ascertain the current state of the data transfer.

**Exception:** Variable initialization; refer to the overview on the next page.

### Note:

When byte DL 32 (= number 65) is used as interface byte, the specified job request is serviced on an "interrupt-driven" basis, i. e. it is "sandwiched" between the job requests that are already in the request buffer. With job number 65 and ANZ > 1, the interrupt job is executed completely.

FB 61: NCD-LESE, FB 62: NCD-SCHR Read NC Data; Write NC Data

ANZ Number of data words to be transferred. If more than one word is transferred (ANZ > 1), both source and destination addresses are incremented. If this results, for example, in addressing of a data word that is no longer available, the PLC goes to STOP with % 2.

Note that a different number of data words is required for each value transferred, depending on the ZFPN parameter.

### **Exceptions:**

When ANZ is 0 or 128, the NSBY, ANZ, WER1-WER3, ZFPN and ZIEL/QUEL parameters are initialized over flag words. The information presented in 5. below (Variable initialization) discusses the difference between ANZ = 0 and ANZ = 128.

DTY1 2 to 6 ASCII characters; CL800 mnemonics.

**DTY3** The values must be input, beginning with DTY1.

### Note:

Unused positions must be padded with blanks. Refer to the table in Section 7.

**ZFPN** PLC/NC number format

Refer to Section 6 for details on the PLC/NC number format

ZIEL Data destination in the PLC (FB 61)

QUEL Data source in the PLC (FB 62)

High byte : DB number (2-255); exception: 0 = flag

Low byte : - Word number (for data blocks)

- Byte number (for flags), (136-255 permitted)

### Note:

1. The number of bytes required must accord with the ZFPN parameter.

2. If, for example, a 16-bit word is to be passed to the NC, the value, when transferred, must be written from data words into the initialized word k + 1 when number formats FO-FF are needed

The parameterized word k has to be set to 0 (see Section 6).

### 5. Variable initialization

When the variable initialization option is used, the values must be written into the flag words in the same format as for direct initialization in the FB.

### Example:

The following must be programmed to initialize the ZFPN parameter with F1:

L KSF1

T FW252

### **Exception:**

The NSBY parameter can be initialized in one of two ways.

When ANZ = 0, the number of the interface byte must be entered in <u>FB 242</u> (refer to Section 1.5, Interface Description).

| No. of the interface byte |          | Byte number |

|---------------------------|----------|-------------|

| 1                         | <u> </u> | DLO         |

| 2                         | ≙        | DRO         |

| •                         |          | •           |

| •                         |          | •           |

| •                         |          | •           |

| 64                        |          | DR31        |

| 65 (interrupt-driven)     |          | DL32        |

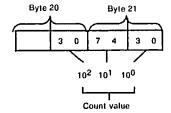

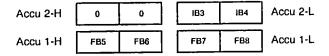

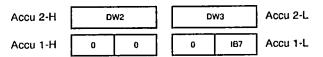

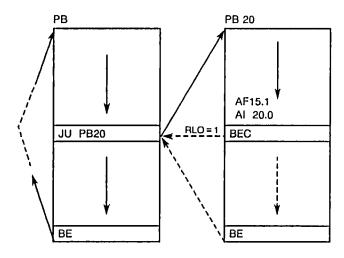

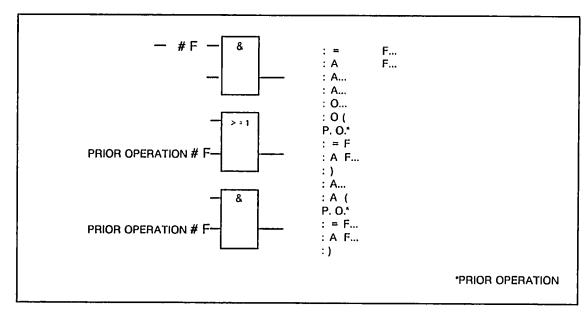

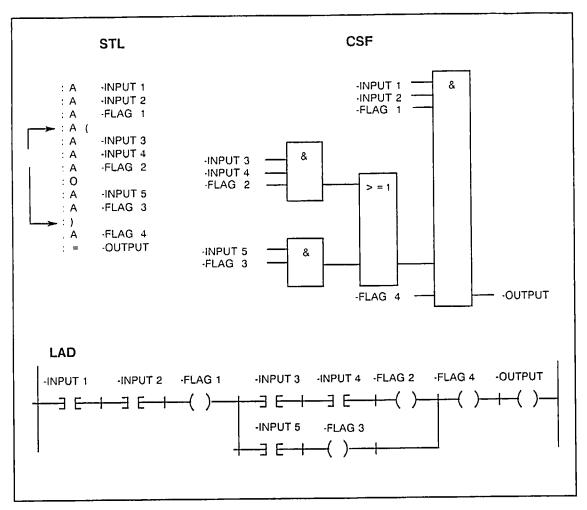

### **Example:**