# SIEMENS

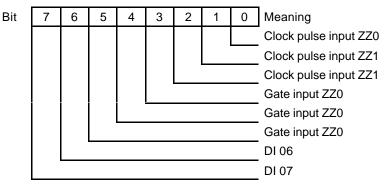

Technical Description Order No.: 6AR1930-0AA07-2CA0

February 2001

## SMP16-CPU06x

SMP16-CPU065, SMP16-CPU066

## SMP16-AT CPU Boards with Pentium II/III Processor

**SICOMP Industrial Microcomputer**

(4)J31069-D2085-U001-A2-7618

| Release <sup>1)</sup> | Overview of Changes          | Date of<br>Release |

|-----------------------|------------------------------|--------------------|

| AO                    | First edition                | 11/99              |

| A1                    | Addition of KS02 functions   | 07/00              |

| A2                    | Addition of the SMP16-CPU066 | 02/01              |

#### List of changes to the technical description

1 Is the 4th block of digits of the drawing number in the footer

#### **Explanation of the notation**

- \* / # An asterisk or a pound character behind the name of a signal indicates a low-active signal (e.g., IOR\* / FRAME#).

- A slash between two signal names separates two level-dependent functions of a signal. (Example: C/D\* means high level for a "command" and low level for "data").

- Connections indicated with a dash in a plug connector allocation table (bus or I/O interface) are reserved.

- **Signal** Special signals not included in the specifications are shown in bold type in the signal allocation tables and then explained at the end (e.g., **NMI**).

Notes:

SICOMP® is a registered brand of Siemens AG.

IBM AT® and IBM PC® are registered brands of International Business Machines Corp.

INTEL® is a registered brand of INTEL Corp.

MS-DOS®, Windows® and Windows NT® are registered brands of Microsoft.

All other designations in this documentation may be brands whose use by third parties for their own purposes may violate the rights of the owner.

Passing on and duplication of this document as well as use and revelation of its contents is not permitted without express permission. Violators will be subject to damage claims. All rights reserved, particularly in the event a patent is granted or a utility model is registered.

With respect to freedom from rights of third parties, no liability is assumed for the specified circuits, descriptions and tables. Technical descriptions specify products but do not guarantee characteristics. The product described in this documentation may require licensing. Please check with your Siemens office.

Subject to delivery capacity and technical changes without prior notice

TD1/Ka/WW8.0/VS5.0/A4

## Notes on safety for SICOMP boards

#### **Qualified personnel**

A device may only be commissioned and operated by **qualified personnel**. For the purposes of the safety notes in this manual, qualified personnel are persons who are authorized to commission, ground and tag devices, systems and electrical circuits in accordance with safety standards.

### **ESD** protective measures

#### Caution

Always adhere to ESD (Electrostatic Sensitive Device) guidelines when handling boards and other components marked with this symbol.

- Never touch the boards unless necessary work makes this unavoidable.

- When handling the boards, use a conductive and grounded work surface.

- Wear a grounding bracelet.

- Never touch chip pins, component connections or circuit board conductors when handling the boards.

- Never allow boards or components to touch chargeable objects (plastics).

- Never place components or boards in the vicinity of cathode ray tube units or television sets (minimum distance: 10 cm).

- Leave the boards in their special packaging until you are ready to use them. Do not take the boards out of their packaging or touch them when registering them and so on.

- Boards may only be installed or removed when the power is off.

#### Wiring of bus backplanes

System-related signal wiring is done with wrap connections for SICOMP board systems. The power supply cables are plug-in or screw-type connections which are bundled together with cable binders.

#### Attention

Keep all signal wiring (particularly the interrupt signal lines) as short as possible. If long signal cables cannot be avoided, use twisted pair wiring.

#### **Related SICOMP literature**

See the SICOMP IMC system manual for more information on installing and handling SICOMP boards.

## **Table of Contents**

| 1 | Introduction                                                                |                                                                                                                                                                                      | 9                                            |

|---|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2 | Technica                                                                    | al Data                                                                                                                                                                              | 11                                           |

| 3 | Initial Co                                                                  | ommissioning                                                                                                                                                                         | 15                                           |

|   | 3.1                                                                         | Settings on the Hardware                                                                                                                                                             | 16                                           |

|   | 3.2<br>3.2.1<br>3.2.2                                                       | Layout and Special Wiring of the Bus Backplane<br>SMP16-CPU065<br>SMP16-CPU066                                                                                                       | 17<br>17<br>18                               |

|   | 3.3                                                                         | Switching from SMP16-CPU055 to SMP16-CPU065                                                                                                                                          | 19                                           |

|   | 3.4                                                                         | Scope of Delivery                                                                                                                                                                    | 21                                           |

| 4 | Features                                                                    | S                                                                                                                                                                                    | 23                                           |

|   | 4.1                                                                         | Microprocessor                                                                                                                                                                       | 26                                           |

|   | 4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                     | Memory<br>BIOS<br>Working Storage<br>Serial EEPROM<br>SRAM Memory                                                                                                                    | 26<br>26<br>26<br>26<br>26                   |

|   | 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8 | Chip Set<br>Power Management<br>System Management Bus<br>Counters and Timers<br>DMA Controller<br>Interrupt Controller<br>NMI Generation<br>Bus Timing<br>Addressing the Loudspeaker | 27<br>27<br>27<br>28<br>28<br>31<br>32<br>32 |

|   | 4.4                                                                         | Drive Controller                                                                                                                                                                     | 33                                           |

|   | 4.5                                                                         | LAN Controller                                                                                                                                                                       | 34                                           |

|   | 4.6                                                                         | VGA Graphics Expansion                                                                                                                                                               | 34                                           |

|   | 4.7<br>4.7.1<br>4.7.2<br>4.7.3                                              | Realtime Functions<br>Additional Counter/Timer Block<br>Additional Interrupt Controller<br>Digital Inputs/Outputs                                                                    | 41<br>41<br>43<br>44                         |

|   | 4.8<br>4.8.1<br>4.8.2<br>4.8.3<br>4.8.4<br>4.8.5<br>4.8.6                   | Safety Functions<br>Voltage Monitoring<br>Battery Buffering<br>Watchdog<br>Temperature Monitoring<br>Password Protection<br>LEDs                                                     | 45<br>45<br>45<br>46<br>46<br>46             |

|   | 4.9<br>4.9.1<br>4.9.2                                                       | Operation without Fan<br>Setting via Setup<br>Regulated Operation                                                                                                                    | 48<br>48<br>48                               |

5

| 4.10<br>4.10.1                                                     | Operational Values<br>Operational Values of theSMP16-CPU06x                                                                                                                                                                                                                  | 49<br>49                                    |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 4.11<br>4.11.1<br>4.11.2<br>4.11.3                                 | System Configuration<br>System Layout of the SMP16-CPU065<br>System Layout of the SMP16-CPU066<br>Operation of SMP16 Boards                                                                                                                                                  | 50<br>50<br>52<br>53                        |

| 4.12                                                               | Overview of the Interfaces                                                                                                                                                                                                                                                   | 55                                          |

| 4.13                                                               | Ambient Conditions                                                                                                                                                                                                                                                           | 56                                          |

| 4.14                                                               | Recommended Accessories/Replacement Parts                                                                                                                                                                                                                                    | 57                                          |

| 4.15                                                               | Recommended Reading                                                                                                                                                                                                                                                          | 58                                          |

| Interfa                                                            | Ces                                                                                                                                                                                                                                                                          | 60                                          |

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                            | Bus Interfaces<br>Signals of the IPCI Socket Strip<br>Signals of the CPCI Socket Strip<br>Signals on the SMP16 Bus<br>Special Signals of the SMP16 Bus                                                                                                                       | 60<br>60<br>61<br>63<br>64                  |

| 5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                   | Drive Interfaces<br>Signals of the UNI-I/O Interface (SMP16-CPU065)<br>Signals of the Rear Panel I/O Interface (SMP16-CPU066)<br>Signals of the Hard Disk Interface (40-Pin)<br>Signals of the Hard Disk Interface (44-Pin)<br>Signals of the Floppy Disk Interface (34-Pin) | 66<br>66<br>67<br>68<br>69<br>70            |

| 5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.3.7 | Front Plate Interfaces<br>USB Bus Interfaces<br>Signals of the Keyboard Interface<br>Signals of the Serial Interfaces - COM A / COM B<br>Signals of the LAN Interface (RJ45)<br>Parallel Interface - LPT1<br>CRT/LVDS Connection<br>PanelLink Connection                     | 71<br>71<br>72<br>72<br>73<br>74<br>75      |

| Comm                                                               | issioning                                                                                                                                                                                                                                                                    | 76                                          |

| 6.1                                                                | Wiring of the Power Supply                                                                                                                                                                                                                                                   | 76                                          |

| 6.2                                                                | Settings on the Hardware                                                                                                                                                                                                                                                     | 77                                          |

| 6.3                                                                | Deleting the CMOS Configuration                                                                                                                                                                                                                                              | 81                                          |

| 6.4                                                                | Wiring of the Interrupts                                                                                                                                                                                                                                                     | 82                                          |

| 6.5                                                                | Changing the Fuses                                                                                                                                                                                                                                                           | 82                                          |

| Notes                                                              | on Programming                                                                                                                                                                                                                                                               | 84                                          |

| 7.1                                                                | Memory Address Areas                                                                                                                                                                                                                                                         | 84                                          |

| 7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6          | Input/Output Address Areas<br>Input/Output for Internal Board Registers<br>Manual Throttling Register<br>General Purpose Ports (GPP)<br>SMB Register Set<br>Memory Input/Output on the SMP16 Bus<br>Direct Input/Output for SMP16 AT Boards                                  | 86<br>88<br>103<br>104<br>105<br>108<br>109 |

| 1.2.0                                                              | Direct input/Output for SMP to AT Boards                                                                                                                                                                                                                                     | 109                                         |

6

7

|    | 7.2.7            | Direct Input/Output for SMP16 I/O Boards                                                             | 110        |

|----|------------------|------------------------------------------------------------------------------------------------------|------------|

| 8  | Driver S         | Software                                                                                             | 112        |

|    | 8.1              | LAN Drivers                                                                                          | 112        |

|    | 8.2              | Graphics Drivers                                                                                     | 112        |

|    | 8.3              | IOS                                                                                                  | 113        |

|    | 8.4              | LAN Boot BIOS                                                                                        | 113        |

|    | 8.5              | Board Support Package                                                                                | 113        |

| 9  | BIOS             |                                                                                                      | 114        |

|    | 9.1              | BIOS Setup                                                                                           | 114        |

|    | 9.1.1            | Starting Setup                                                                                       | 114        |

|    | 9.1.2            | Exiting Setup                                                                                        | 117        |

|    | 9.1.3<br>9.1.4   | Setup Page - "Standard CMOS Setup"<br>Setup Page - "BIOS Features Setup"                             | 118<br>121 |

|    | 9.1.4<br>9.1.5   | Setup Page - "Chipset Features Setup"                                                                | 121        |

|    | 9.1.6            | Setup Page - "Power Management Setup"                                                                | 126        |

|    | 9.1.7            | Setup Page - "PNP/PCI Configuration"                                                                 | 128        |

|    | 9.1.8<br>9.1.9   | Setup Page - "Load BIOS Defaults" and "Load Setup Defaults"<br>Setup Page - "Integrated Peripherals" | 130<br>131 |

|    | 9.1.9<br>9.1.10  | Setup Page - "IMC Miscellaneous"                                                                     | 133        |

|    | 9.1.11           | Setup Page - "Password Setting"                                                                      | 135        |

|    | 9.1.12           | Setup Page - "IDE HDD Auto Detection"                                                                | 135        |

|    | 9.1.13<br>9.1.14 | Setup Page - "Save & Exit Setup"<br>Setup Page - "Exit Without Saving"                               | 136<br>137 |

|    | 9.1.14<br>9.1.15 | Setup - Default Setting                                                                              | 137        |

|    | 9.2              | LAN Boot BIOS                                                                                        | 141        |

|    | 9.3              | BIOS Flash Memory                                                                                    | 142        |

|    | 9.4              | ROM-BIOS Interrupts                                                                                  | 143        |

|    | 9.5              | BIOS Data Area                                                                                       | 145        |

| 10 | BIOS U           | pdate                                                                                                | 148        |

|    | 10.1             | System BIOS                                                                                          | 148        |

|    | 10.2             | The AWDFLASH.EXE Service Program                                                                     | 148        |

|    | 10.3             | How To Update Your BIOS                                                                              | 149        |

|    | 10.3.1           | System with Graphics Card                                                                            | 149        |

|    | 10.3.2           | System with Console Rerouting without Graphics Card                                                  | 149        |

| 11 | BSP-CP           | PU06x: RMOS on the SMP16-CPU06x                                                                      | 150        |

|    | 11.1             | RMOS and Power Management/Fanless Operation                                                          | 150        |

|    | 11.2             | Installation Program                                                                                 | 151        |

|    | 11.3             | RMOS Configuration for the SMP16-CPU06x                                                              | 152        |

|    | 11.3.1           | Support of the Secondary EIDE Controller                                                             | 152        |

|    | 11.3.2<br>11.3.3 | TCP/IP Connection<br>Extra Interrupt Controller                                                      | 157<br>158 |

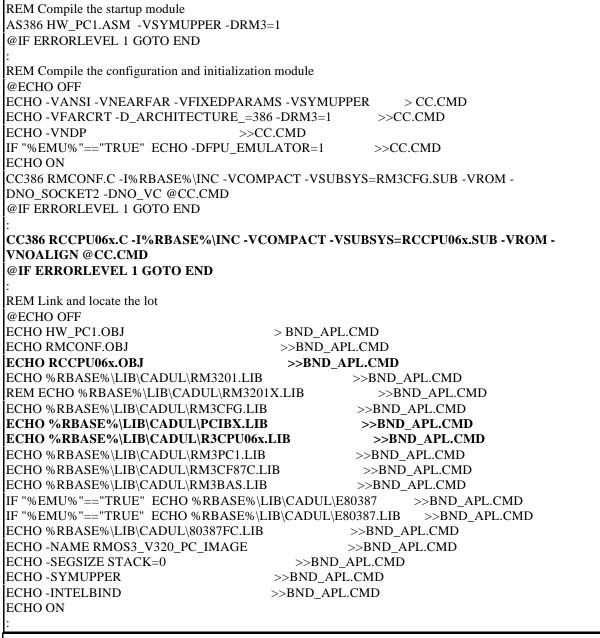

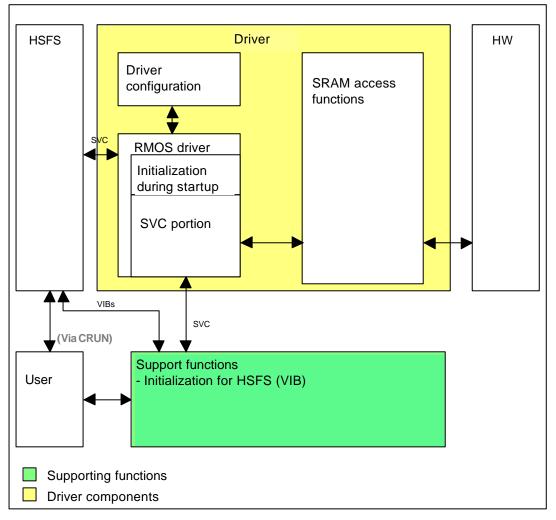

|    | 11.3.4           | SRAM Driver                                                                                          | 159        |

|    | 11.3.5           | System Generation                                                                                    | 162        |

|    |                  |                                                                                                      |            |

|    | 11.4   | Additional Functions                        | 165 |

|----|--------|---------------------------------------------|-----|

|    | 11.4.1 | Temperature Monitoring                      | 165 |

|    |        | , .                                         |     |

|    | 11.4.2 | Use of the BIOS Flash Memory                | 166 |

|    | 11.4.3 | Use of the Serial EEPROM                    | 176 |

|    | 11.4.4 | Use of the Buffered SRAM                    | 178 |

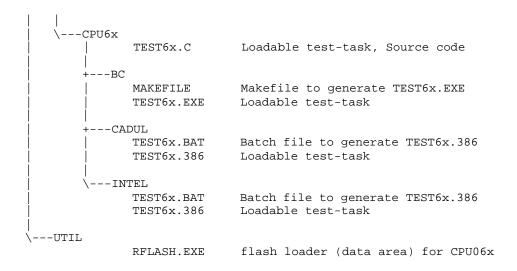

|    | 11.4.5 | Description of test program TEST6x.386      | 192 |

| 12 | Append | dix                                         | 193 |

|    | 12.1   | Notes on the Different Operating Systems    | 193 |

|    | 12.1.1 | Windows NT                                  | 193 |

|    | 12.1.2 | Win9x                                       | 193 |

|    | 12.1.3 | RMOS                                        | 193 |

|    | 12.2   | Layout of the CMOS RAM and the CDT          | 194 |

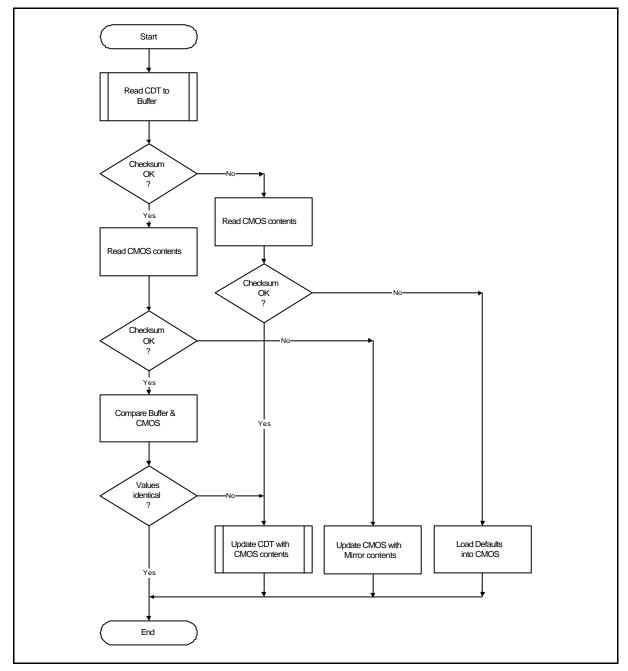

|    | 12.3   | Use of the CDT during BIOS Startup          | 195 |

|    | 12.4   | POST Codes                                  | 196 |

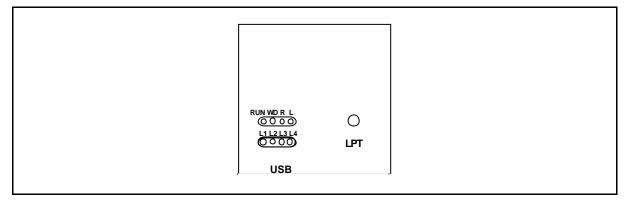

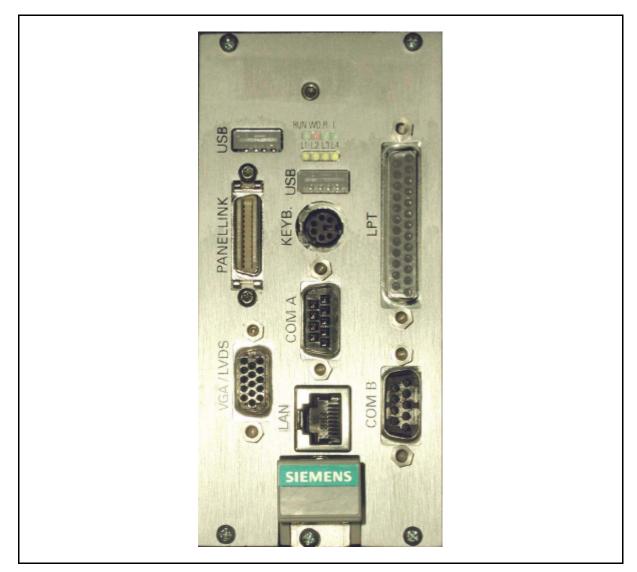

|    | 12.5   | View of the Front Plate of the SMP16-CPU06x | 198 |

|    | 12.6   | Abbreviations and Terms                     | 200 |

## 1 Introduction

The functions of the two SICOMP IMC SMP16 CPU boards are the same. The only difference is the PCI bus connection with the applicable I/O expansions.

A description of the functionality of the SMP16-CPU066 has been added to the existing technical description (release A1, July 2000).

Another difference is the decoupling of the secondary EIDE channel and floppy via the I/CPCI backplane. With the CPCI backplane, the signals for the secondary EIDE channel and the floppy disk drives are assigned to the area for the rear panel I/O. An adapter is required to decouple these signals (see chapter 4.14).

Use of the SMP16-CPU065 varies depending on the specific models of the individual boards, while such differentiation does not apply with the SMP16-CPU066!

The SMP16-CPU066 does not have a PCI-PCI bridge which means that the CPCI backplane bus is PCI bus 0 of the SMP16-CPU066.

## 2 Technical Data

## SMP16-CPU06x without AGP option

| Processor                      | Pentium II starting at 266 MHz<br>(333 MHz SMP16-CPU066)<br>Pentium III starting at 500MHz                                            |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Numeric processor              | Integrated in the processor                                                                                                           |

| Cache                          | 32 kbytes integrated in the processor<br>256/512-Kbyte, synchronous, second-level cache -<br>external or integrated dep. on processor |

| Main memory                    | 64 to 256-Mbyte SDRAM (dep. on availability)<br>1 slot for 64/128/256-Mbyte -modules<br>JEDEC 144 pin SO DIMM, 3,3V                   |

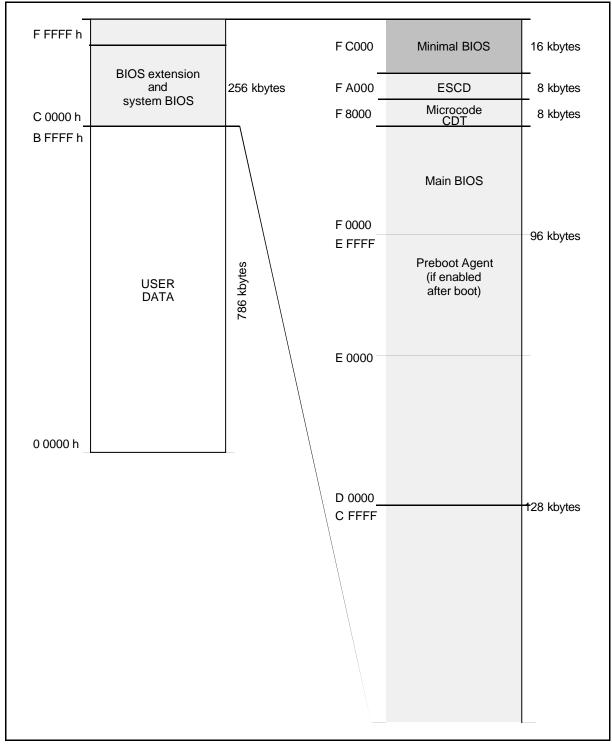

| ROM memory (flash EPROM)       | Total of 1 Mbyte<br>256 kbytes for system and LAN-BIOS<br>768 kbytes for user data                                                    |

| SRAM memory                    | 128 kbytes buffered, briefly via gold CAP,<br>otherwise via battery on system rack                                                    |

| Network                        | AMD 79C793 10/100 MBaud network controller<br>Automatic 10BaseT/100BaseT2 switchover                                                  |

| Realtime expansions            |                                                                                                                                       |

| Interrupt system               | Interrupt controller 82C59A,<br>Five inputs accessible by SMP16 bus<br>Five inputs accessible by SMP16 bus                            |

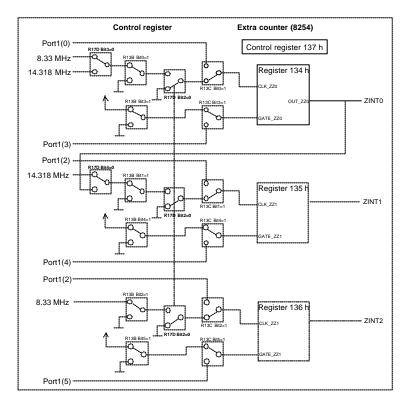

| Counter/timer                  | Timer 82C54,<br>Outputs connected to interrupts<br>Gate and clock pulse inputs configurable                                           |

| Connections                    |                                                                                                                                       |

| PS/2 mouse/keyboard connection | Mini DIN socket, 6-pin                                                                                                                |

| Parallel interface             | Socket, 25-pin, bidirectional, EPP/ECP capability                                                                                     |

| Two serial interfaces          | Plug connector, 9-pin, 16550-compatible                                                                                               |

| USB (Universal Serial Bus)     |                                                                                                                                       |

| LAN (Local Area Network)       | RJ45 socket                                                                                                                           |

| SMP16 Bus                      | 96-pin pin strip, in acc. w. DIN 41694,                                                                                               |

- Hard disk interfaces

(EIDE, UDMA33)

- Floppy disk interfaces

96-pin pin strip, in acc. w. DIN 41694, allocated in acc. w. SMP16 bus spec. V1.0

40-pin pin strip (channel 0) and Expansion of the I/CPCI bus (channel 1)

34-pin pin strip (drive A) and Expansion of the I/CPCI bus (drive B)

- 16 digital inputs/outputs

2 10-pin socket strips, AMP Micro Match, parameterizable, TTL level

SMP16-CPU065

IPCI bus

180-pin socket strip Allocated in acc. w. IPCI bus spec. V1.51, July 1998

- channel) and floppy disk interface (drive B) SMP16-CPU066: - CPCI bus 220-pin socket strip Allocated in acc. w. CPCI spec. PICMG 2.0 R3.0 RPIO allocation for hard disk interface (secondary channel) and floppy disk interface (drive B)

UNI-IO allocation for hard disk interface (secondary

#### AGP option

•

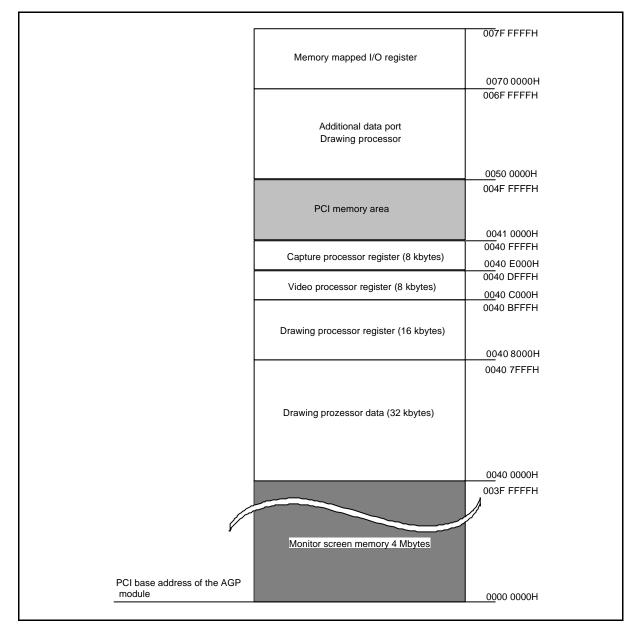

| Monitor screen controller           | Silicon Motion LYNX E/EM                |

|-------------------------------------|-----------------------------------------|

| Video memory (SG-RAM)               | 4 Mbytes                                |

| Monitor screen resolution supported | 1024 x 768/16.7 million colors at 75 Hz |

#### Connections

USB

•

| • | Analog monitor screen/<br>LVDS display | Socket, 15-pin, high density<br>Can be switched for display<br>Resolution: 640x480 / 800x600 / 1024x768 |

|---|----------------------------------------|---------------------------------------------------------------------------------------------------------|

| • | PanelLink display                      | Socket, 26-pin HDP<br>Resolution: 640x480 / 800x600 / 1024x768                                          |

©Siemens AG 2001, All Rights Reserved (4)J31069-D2085-U001-A2-7618

| Power consumption               |                       |                                                                                  | Starting at 20 W                                                                                                                                             |  |  |

|---------------------------------|-----------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Permissible ambient temperature |                       |                                                                                  |                                                                                                                                                              |  |  |

| •                               | Operation             |                                                                                  | 0 °C to 55 °C<br>With fan, 3 x 100 m <sup>3</sup> /h<br>With "no fan" setting in BIOS Setup                                                                  |  |  |

| •                               | Transportation        |                                                                                  | -40° C to 70° C                                                                                                                                              |  |  |

| Phy                             | sical stress          |                                                                                  |                                                                                                                                                              |  |  |

| •                               | Vibration             | Operation                                                                        | 2 g, 20 cycles per axis, 1 octave per min<br>In acc. w.: DIN EN 60068-2-6 Test Fc                                                                            |  |  |

| •                               | Shock                 | Operation                                                                        | 30 g, half-sine 11 msec, pos. and neg.,direction:<br>3 shocks per axis                                                                                       |  |  |

|                                 |                       | Storage                                                                          | In acc. w.: DIN EN 60068-2-27 Test Ea<br>25 g, half-sine, 6 msec, pos. and neg., direction:<br>1000 shocks per axis<br>In acc. w.: DIN EN 60068-2-29 Test Eb |  |  |

| Electromagnetic compatibility   |                       | ibility                                                                          | Generic standard (EMC for industry)<br>In acc. w.: EN50081-2:1993<br>EN50082-2:1995                                                                          |  |  |

| Din                             | nensions (width, dept | h, height)                                                                       | 40/60 mm, 180 mm, 130 mm                                                                                                                                     |  |  |

| We                              | ight                  |                                                                                  | Approx. 1.5 kg with AGP option<br>Approx. 1.3 kg without AGP option                                                                                          |  |  |

| Rel                             | iability (MTBF)       | With AGP, with SM<br>With AGP, without<br>Without AGP, with<br>Without AGP, with | SMP16 29.4 years                                                                                                                                             |  |  |

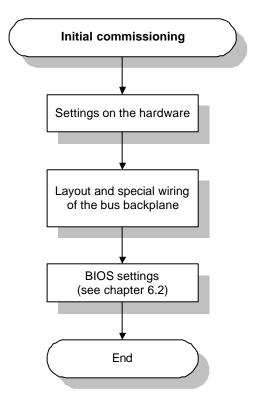

## 3 Initial Commissioning

The flowcharts on the next few pages illustrate the procedure recommended for initial commissioning of the board.

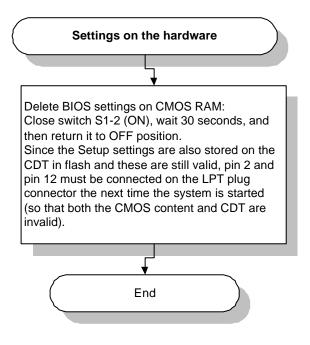

## 3.1 Settings on the Hardware

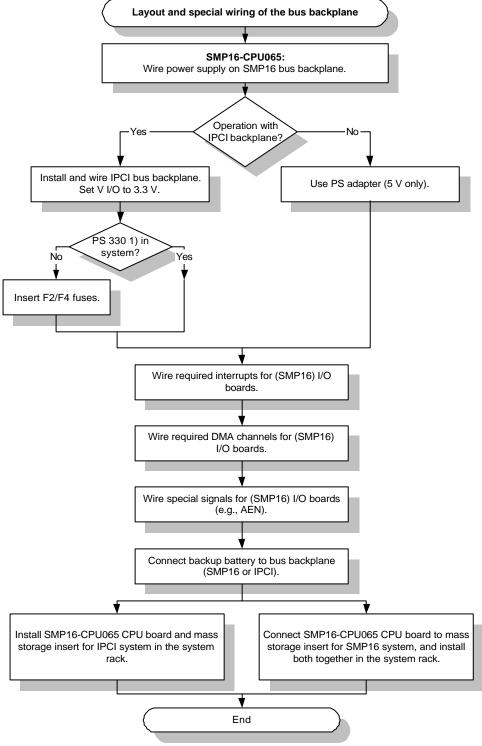

## 3.2 Layout and Special Wiring of the Bus Backplane

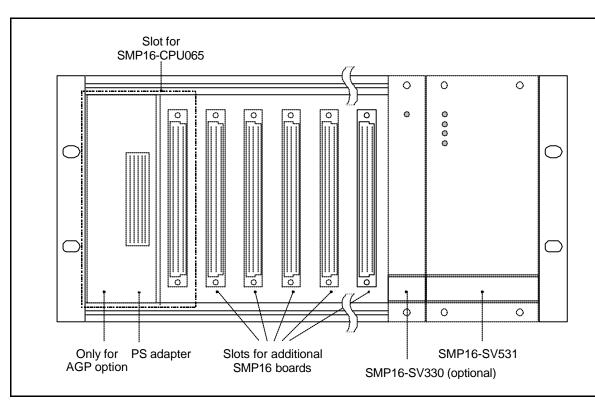

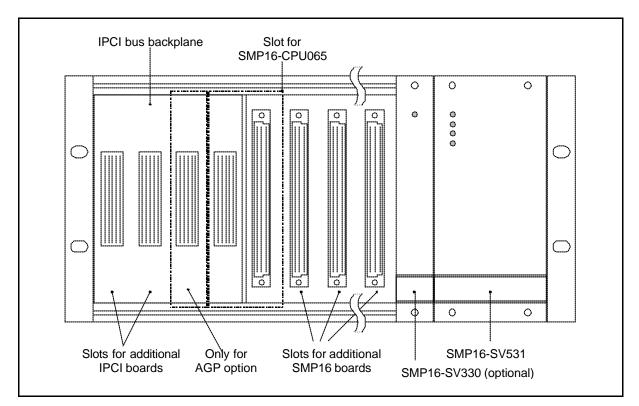

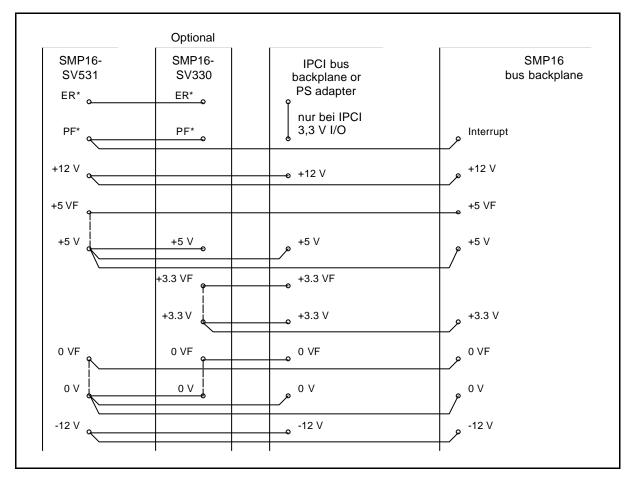

## 3.2.1 SMP16-CPU065

1) PS 330 is required if PCI boards need 3.3 V.

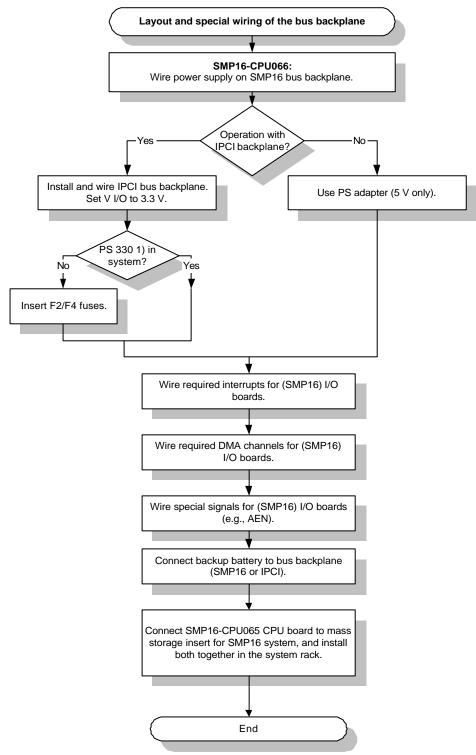

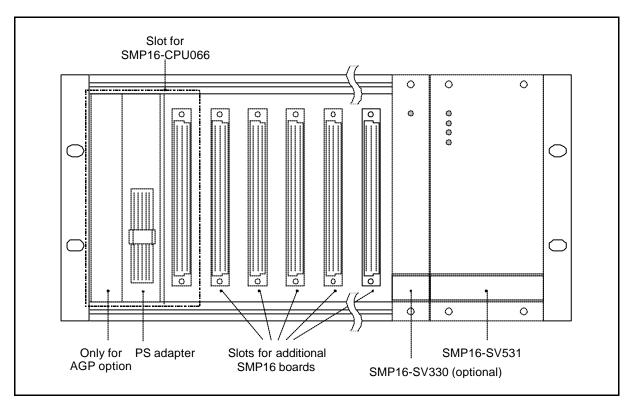

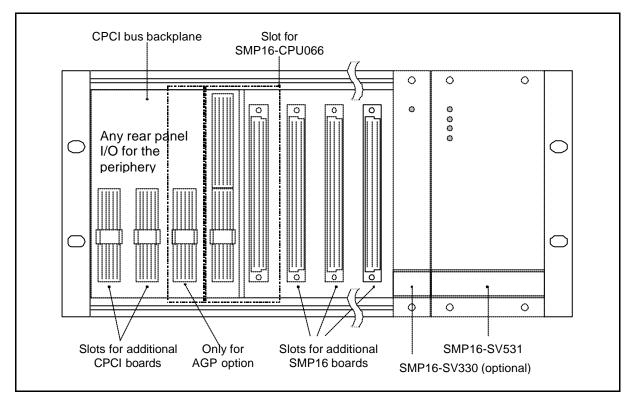

## 3.2.2 SMP16-CPU066

1) PS 330 is required if PCI boards need 3.3 V.

## 3.3 Switching from SMP16-CPU055 to SMP16-CPU065

Keep the following points in mind when switching from an SMP16-CPU055 to an SMP16-CPU065 in an existing SMP16 system.

- The SMP16-CPU065can be installed directly in the slot of the SMP16-CPU055.

- The IPCI bus plug connector must at least be powered with the PS adapter (only 5 V required).

- When an IPCI backplane and IPCI cards are used, the backplane must be wired. Remember that the 3.3 volts from the SMP16-CPU065 are not available to the IPCI bus.

- The VIO (reference voltage for the signal level on the IPCI bus) must be set to 3.3 V. All IPCI I/O boards must use the VIO of the backplane bus.

- When an IPCI backplane with HD/FD-UNI-I/O wiring is used, one slot should be left free on the left side to leave room for the new design (new drive insert).

The table below shows the differences between the SMP16-CPU065 and the SMP16 CPU055

| Function                                                                    | SMP16-CPU055                                                                    |                                                                                                                                      | SMP                                                                      | P16-CPU065                                                                                                |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 3.3 volt power supply                                                       | Required from external source. Feed<br>in over PS adapter or IPCI<br>backplane. | On boa                                                                                                                               | ard                                                                      |                                                                                                           |

| SMP16 register can be read back.                                            | No                                                                              | 0178h<br>Startir                                                                                                                     | isters can be<br>to 017Fh.<br><b>1g with KS02</b><br>rea 0138h to        |                                                                                                           |

| SMP16 bus interface can be switched off.                                    | No                                                                              |                                                                                                                                      | 78 bit 7 = 1.<br>(Also switch o                                          | off SYSCLK/OSC)                                                                                           |

| Switch off clock pulses<br>on the SMP16 bus<br>(8.33 MHz and<br>14.318 MHz) | No                                                                              | Startir                                                                                                                              | 78 bit 6 = 1.<br>(Bit 7 = 0 req<br><b>ng with KS0</b> 2<br>R13B bit 6, 7 | uired)                                                                                                    |

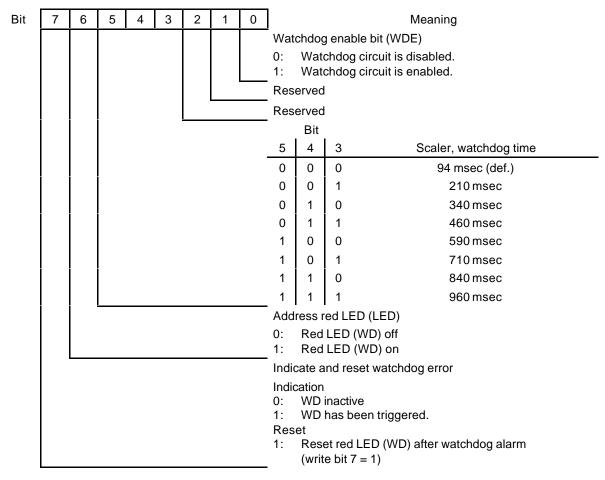

| Watchdog can be read back.                                                  | No                                                                              | R17E bit 7 = 1 after restart (no power on)<br>indicates that a watchdog reset took place.<br>Writing R17E bit 7 = 1 deletes the bit. |                                                                          |                                                                                                           |

| Watchdog time can be set.                                                   | Two times (approx. 100 msec, 1 sec)                                             | Adjustable between 96 msec and 960 msec<br>R17E Bit 3,4,5                                                                            |                                                                          | n 96 msec and 960 msec                                                                                    |

| Additional counter block                                                    | No                                                                              | Access via R134-R137                                                                                                                 |                                                                          |                                                                                                           |

|                                                                             |                                                                                 |                                                                                                                                      | Bit 3, 4<br>Bit 4                                                        | Input clock pulse counter,<br>ZZ0 and ZZ1 can be set.<br>Cascading of<br>counters ZZ0 and ZZ1<br>possible |

|                                                                             |                                                                                 | R17C                                                                                                                                 |                                                                          | Counter enable                                                                                            |

|                                                                             |                                                                                 |                                                                                                                                      | ng with KS02                                                             |                                                                                                           |

|                                                                             |                                                                                 | R13B                                                                                                                                 | Bits 0,1,2                                                               | Clock pulses can be<br>enabled separately.                                                                |

|                                                                             |                                                                                 |                                                                                                                                      | Bits 3, 4, 5                                                             | Gates can be addressed separately.                                                                        |

|                                                                             |                                                                                 | R13C                                                                                                                                 | ,                                                                        | Clock pulses can be<br>addressed with DI.                                                                 |

|                                                                             |                                                                                 |                                                                                                                                      | Bits 4,5,6                                                               | Gates can be addressed with DI.                                                                           |

| Function                             | SMP16-CPU055                                                     | SMF                                                                                           | P16-CPU065                                                                                          |  |

|--------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Interrupt matrix for                 | No                                                               | Electronic interrupt                                                                          | matrix                                                                                              |  |

| additional interrupt block           |                                                                  | R178 Bit 0,1,2                                                                                | Interrupt enable and selection                                                                      |  |

| Additional interrupt block           | No                                                               | Controller for various events (outputs of additional counters, DREQ signals of the SMP16 bus) |                                                                                                     |  |

|                                      |                                                                  | R130/131<br>R133 read                                                                         | Registers of the extra<br>8259 (ICW, OCW)<br>INTA add. 8259                                         |  |

| Cascaded interrupts on the SMP16 bus | No                                                               | Starting with KS0<br>Additional interrupt<br>can be cascaded.<br>R178 Bit 3                   | 2:<br>controller on SMP16 bus<br>Enable CAS_EN                                                      |  |

| Buffered SRAM                        | No                                                               | Maximum of 128 kt                                                                             | oytes                                                                                               |  |

|                                      |                                                                  | R17A                                                                                          | Base address                                                                                        |  |

|                                      |                                                                  | R17D Bit 5, 6, 7                                                                              | Enable and length of the window.                                                                    |  |

| Digital inputs/outputs,<br>TTL level | No                                                               | Starting with KS0<br>wo 8-bit ports can b<br>or output.                                       | <b>2:</b><br>be parameterized as input                                                              |  |

|                                      |                                                                  | R138/9<br>R13A                                                                                | Data ports<br>Control regis ter<br>set as clock pulse and gate<br>onal counter.<br>Parameterization |  |

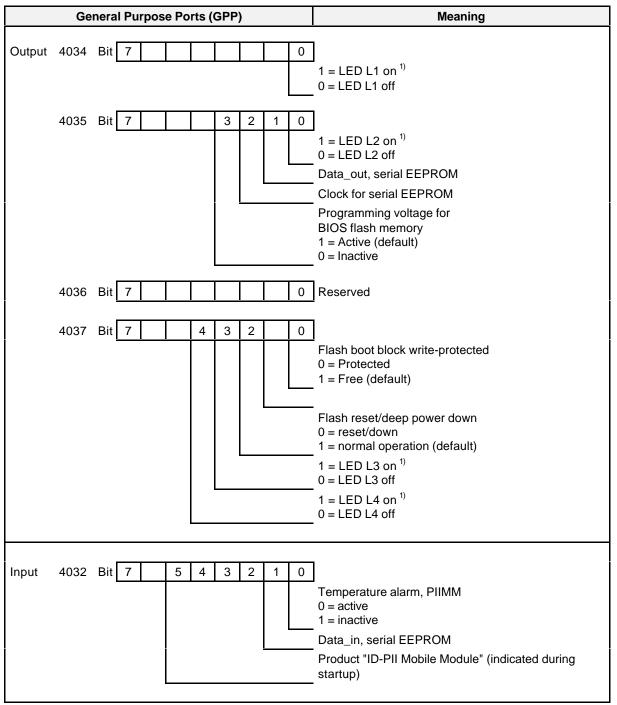

| Serial EEPROM                        | Access via GPP2 of the FDC37C932                                 | Access via GPP2 of                                                                            | f the PIIX4E                                                                                        |  |

|                                      | (0EAh/0EBh bits 0 to 2: DI, DO,<br>CLK)                          | R4035 Bit 2:<br>EEPROM                                                                        | Clock pulse for ser.                                                                                |  |

|                                      |                                                                  | R4035 Bit 1<br>(GPO9)                                                                         | (GPO10)<br>Data for ser. EEPROM                                                                     |  |

|                                      |                                                                  | R4032 Bit 1                                                                                   | Data from ser. EEPROM<br>(GPI17)                                                                    |  |

| USER LED                             | Two LEDs can be addressed via GPIO of the FDC37C932, can be      | Four LEDs can be indications (via BIC                                                         |                                                                                                     |  |

|                                      | used (via jumper) for the hard disk channels to indicate access. | R17C Bit 0-3                                                                                  |                                                                                                     |  |

|                                      |                                                                  | USER LED can be<br>PIIX4E.<br>R4034 Bit 0                                                     | address via GPO of<br>LED 0 (GPO0)                                                                  |  |

|                                      |                                                                  | R4035 Bit 1<br>R4037 Bit 3<br>R4037 Bit 4                                                     | LED 1 (GP08)<br>LED 2 (GP027)<br>LED 3 (GP028)                                                      |  |

| SMP_INT                              | Fixed on IRQ15                                                   | channel.                                                                                      | y's sake, IRQ15 is<br>ned to the secondary EIDE<br>be fed in with one of the                        |  |

|                                      |                                                                  | SMP_IRQs.                                                                                     |                                                                                                     |  |

|                                      |                                                                  | SMP_INT is a                                                                                  | the EIDE channel                                                                                    |  |

#### Note:

- Since the Elite BIOS of the SMP16-CPU06x calculates the hard disk parameters differently than the Power BIOS of the SMP16-CPU055 (in LBA mode), the hard disk may have to be reformatted and a new installation performed.

- When an SMP16-CPU055 is to be used instead of anSMP16-CPU06x a 3.3 V power supply is mandatory.

## 3.4 Scope of Delivery

The SMP16-CPU06x is delivered with or without AGP expansion based on your order. The model without the AGP option requires two slots while the version with the AGP option needs three slots.

The IPCI-CPU066 or CPCI-CPU066 is the same as SMP16-CPU06x but without an SMP16 bus interface board. This means the following functions are not available.

- Additional interrupt controller

- Additional counter block

- Buffered SRAM

The SMP16-CPU06x no longer includes a power supply adapter (PS adapter) for providing the 5 Volt on the IPCI/CPCI bus connection. It must be ordered separately. The PS adapter is not required when an IPCI(CPCI backplane is used.

Two fuses for the VIO supply of the backplane are included with the SMP16-CPU065 . These fuses must be installed when no 3.3 V voltage supply is available in the system and thus there is also no 3.3 V VIO reference voltage for the IPCI bus.

If this is the case, switches S1-3/4 must be closed on the SMP16-CPU066. The VIO jumper on the CPCI backplane must be set to 3.3 Volt.

## 4 Features

The SMP16-CPU06x is an IBM-PC/AT-compatible CPU board for use on SICOMP-SMP16 industrial microcomputers. It has a metal front for individual locking. It requires two or three slots depending on the model.

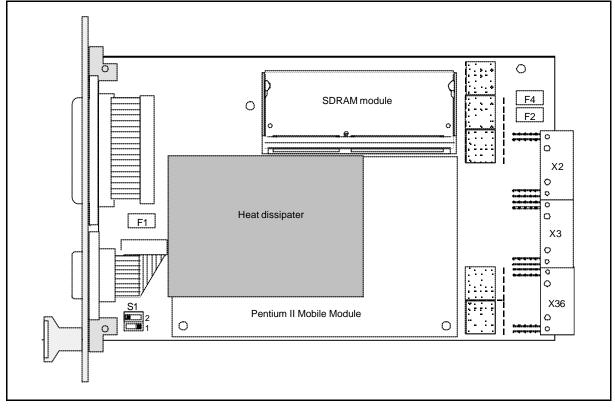

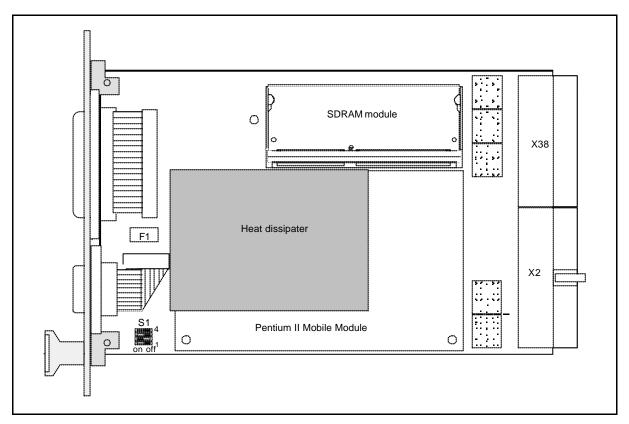

The board is of sandwich design consisting of the following (depending on the model).

- <u>AGP model</u> (as seen from the front)

- Left = AGP board

- Middle = CPU board

- Right = SMP16 bus interface

- <u>Model without AGP</u> (as seen from the front)

- Left = CPU board

- Right = SMP16 bus interface

#### Note:

The SMP16-CPU06x can only be used on SMP16 bus backplanes. SMP bus backplanes are not suitable since they are missing signal lines. Use without an SMP16 bus backplane is possible.

The or IPCI-CPU065 CPCI-CPU066 is the same as the SMP16-CPU06x but without the SMP16 interface for use with IPCI/CPCI systems without SMP16 bus connection. It has a metal front for individual locking. It requires two or three slots depending on the model.

- <u>AGP model</u> (as seen from the front)

- Left = AGP board

- Middle = CPU board

- <u>Model without AGP</u> (as seen from the front)

- Left = CPU board

#### Attention:

The rest of this technical description only describes the **SMP16-CPU06x**. The IPCI-CPU065 or CPCI-CPU066 does not have any of the functions which are implemented on the SMP16 expansion board (SMP16 bus interface, SRAM, timer, additional interrupt controller, digital inputs/outputs, standard drive interfaces).

### Features of the SMP16-CPU06x

- Since the board is equipped with an IPCI bus connection in addition to the SMP16 bus, it can only be installed on the first SMP16 bus slot from the left.

- The board has an U-profile front plate with lever-pull handle and is prepared for EMC contact springs.

- The CPU generates the 3.3 V itself. When additional IPCI/CPCI or SMP16 boards with 3.3 V are used, an extra 3.3 V supply is required.

### CPU board

- Pentium-II/III Mobile Module inside

- Mobile Pentium II/III processor

- Chipset 82440BX from Intel, only North-Bridge (82443 BX)

- Second level cache (L2 cache)

- Power supply for processor core

- DRAM (SDRAM: only synchronous DRAM), max. of 256 Mbytes

- ISA–Bridge (South-Bridge) PIIX4E (82371 EB)

- AMD-LAN controller, 10/100 MBaud (79C 973)

- Clock pulse generation

- DC/DC converter for 3.3 V on board

- BIOS flash, up to 1 Mbyte

- Super I/O block integrated (FDC 37C 672)

- Keyboard controller

- Floppy disk controller

- Serial interfaces

- Parallel interface

- Reset/watchdog logic

- LEDs: RUN, WD, 2 x LAN, 4 x USER

- Bus interfaces

- IPCI/CPCI bus (065/066)

- UNI-I/O with HD/FD signals (secondary drive channel FD: drive B)

- Front plate interfaces

- Combined keyboard/mouse

- USB interface, single

- LAN (RJ45)

- COM A/COM B (RS 232)

- LPT (TTL)

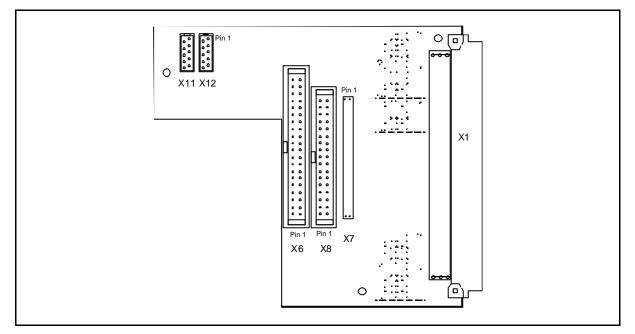

#### SMP16 bus interface (can be ordered as option)

- Additional realtime functions (counter, interrupt controller)

- 128-kbyte buffered SRAM

- SMP16 bus interface

- Drive interfaces for SMP16 drive insert

- Hard disk interface (HD: primary channel)

- Floppy disk interface (FD: drive A)

### AGP board (optional)

- Graphics controller from Silicon Motion LYNX E/EM

- 4-Mbyte video memory (SG-RAM)

- Max. resolution of 1024 x 768 pixels

- Analog VGA interface, alternate LVDS interface (can be changed with switch)

- PanelLink interface

- USB interface

- Voltage supply for PanelLink display

## 4.1 Microprocessor

The **SMP16-CPU06x** is equipped with the 32-bit Intel Pentium-II/III processor with a bus frequency of 66/100 MHz. The PII/III Mobile Module with MMC2 connection is used.

## 4.2 Memory

#### 4.2.1 BIOS

The board's BIOS is stored on a 1-Mbyte flash memory chip. The flash memory is permanently installed and can be reprogrammed on board (see chapter 10).

The BIOS is unpacked during startup (Post C3) and then copied to the DRAM (Post C5) which is shadowed in the memory area in place of the flash memory (shadow RAM function for the E/F segment). This speeds up the BIOS program functions.

The BIOS is compatible with the Elite BIOS V4.51 from the AWARD company. It contains a basic configuration of the board and its own Setup. For details, see chapter 9.3.

#### 4.2.2 Working Storage

A Small Outline DIMM module is used for working storage. SDRAMs are used for optimum performance. The memory module cannot be changed or expanded by the user.

#### 4.2.3 Serial EEPROM

Configuration data are stored on the board's 256-byte EEPROM (type X24C02 (XICOR/ATMEL) with the serial m fC bus interface. The contents of this chip are retained (even without battery backup) after the power supply is turned off. The first 64 bytes are reserved for manufacturer's data and may not be overwritten.

Communication with this chip takes place via three bits in general-purpose port 2 (see chapter 7.2.3). These bits must be addressed as required by the  $^{2}$ C bus protocol. Two address bytes and one data byte must be transferred by bit for each byte to be sent.

#### 4.2.4 SRAM Memory

The SMP16 board offers a 128-kbyte buffered SRAM. The maximum of 128 kbytes can be shadowed via register in various address areas or completely

deactivated (see chapter 9.1.10). A limited choice is available in BIOS Setup.

## 4.3 Chip Set

The AT functions of the **SMP16-CPU06x** are implemented with chip set 82440BX and supplemented with Super I/O chip FDC 37C 672.

| Chip     | Manufacturer | Function                                                                                                                                     |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 82443BX  | Intel        | System controller<br>(DRAM control, PCI bus addressing, AGP bus interface)                                                                   |

| 82371EB  | Intel        | PCIISA-Bridge (PIIX4E)<br>(Hard disk control, interrupt and DMA controller, counter,<br>RTC, CMOS RAM, Power Management, USB, and<br>GP I/O) |

| FD37C672 | SMSC         | Super I/O chip<br>(Floppy disk controller, serial and parallel interfaces,<br>keyboard interface and mouse interface)                        |

## 4.3.1 Power Management

The chipset supports various Power Management functions which can be activated in BIOS Setup. In particular, APM V1.2 (Advanced Power Management) and ACPI (Advanced Configuration Programming Interface - only S1 state) are implemented.

Power Management functions permit you to put the computer into various energy saver states after specified times (see BIOS description).

Operating systems such as Win9x and WinNT are built on these interfaces. These functions can no longer be accessed under RMOS.

## 4.3.2 System Management Bus

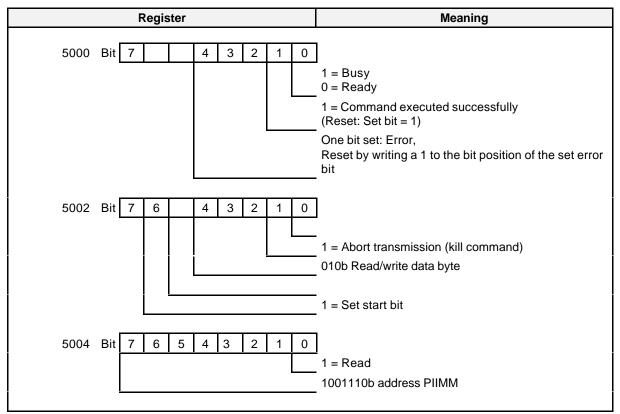

The chipset (PIIX4E) contains a system-management-bus (SMB) host and slave interface. The PIIX4E host interface is used on the **SMP16-CPU06x**. The SDRAM module and the Pentium II Mobile Module are connected to the SMB.

On the PIIMM, both temperature sensors are connected to the SMB. These supply the current temperatures of the processor core and the BX chip.

The host interface is addressed in the I/O area starting at address 5000h (see programming notes in chapter 7).

## 4.3.3 Counters and Timers

The counter/timer unit of the PIIX4E chip has three 16-bit counters (Z0 to Z2) and is compatible with an 8254 chip. The counters have a fixed clock-pulse frequency of 1.193 MHz.

The counters are prewired for IBM-compatible operation.

- The gates of counters Z0 and Z1 fixed at +5 V.

- Counter Z0 generates the system time. Its output is permanently connected with IRQ0 inside the chip (see chapter 4.3.5).

- Counter Z1 initiates the refresh cycle of the DRAM controller. BIOS sets it to a clock pulse duration of 15.6 µsec.

- Counter Z2 is usually used to address a system loudspeaker (see chapter 4.3.8). It can be enabled or disabled with address 61h.

### 4.3.4 DMA Controller

The two 8237-compatible DMA controllers of the PIIX4E provide 8 DMA channels which are circuited like ATs.

| Channel | 8/16 Bits | Function    | Remarks |

|---------|-----------|-------------|---------|

| CH0     | 8         |             | 1)      |

| CH1     | 8         | ECP printer | 2)      |

| CH2     | 8         | Floppy disk | -       |

| CH3     | 8         |             | 1)      |

| CH4     | -         | Cascading   | -       |

| CH5     | 16        |             | 1)      |

| CH6     | 16        |             | 1)      |

| CH7     | 16        |             | -       |

1) The DMA channel is available on the SMP16 bus and can be requested by an external DMA source.

2) Is programmed for LPT standard mode (Setup). <sup>1)</sup> then applies.

Note:

If the cascaded interrupts function of the additional interrupt controller is used in the application with the SMP16-CPU065 starting at KS02, no other DMA channels are available on the SMP16 bus except the DMA channel (DREQ3/DACK3\*).

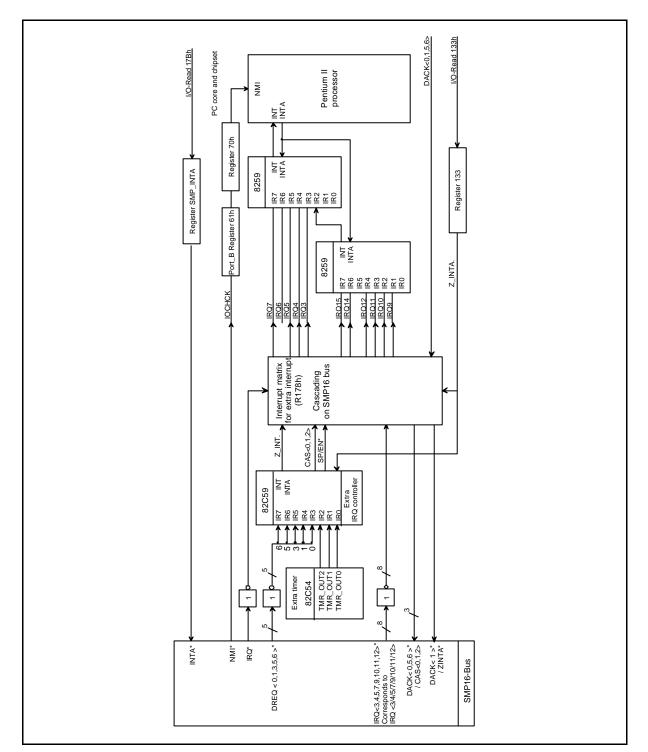

#### 4.3.5 Interrupt Controller

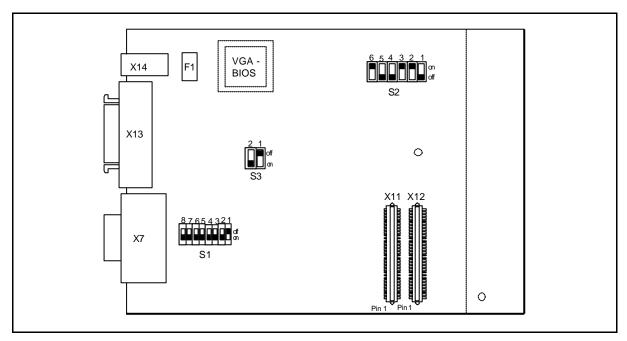

The interrupt controller function is compatible with two cascaded 8259 controllers. They are circuited to be compatible with AT. A total of 14 interrupt inputs are available on PIIX4E. Figure 4.1 shows the circuiting of internal controllers intc1 and intc2 as well as the interface and presettings of the board.

Interrupt INT can be cascaded further on the SMP16 bus. This requires a separate interrupt routine which is explained in the description of the INTA\* generation register in chapter 7.2.1.10.

The unassigned connections of the interrupt controller are connected to the SMP16 bus where they can be wired (see chapter 5.1).

BIOS automatically assigns the PCI interrupts to the available ISA interrupts (maximum of four). These interrupts are then no longer available on the SMP16 bus.

Note:

Various interrupts for automatic routing by BIOS can be disabled in Setup (see Setup in chapter 9.1.7).

#### Attention:

If too many interrupts are disabled (setting Legacy ISA) in BIOS Setup (PnP Configuration) for the automatic routing for PCI components which require an interrupt, additional interrupts may not be able to be assigned to all devices/any devices. These PCI bus components can no longer be used.

#### Configuration on the SMP16-CPU06x (BIOS defaults)

|                         | SMP16-CPU065        | SMP16-CPU066           |

|-------------------------|---------------------|------------------------|

| Secondary EIDE channel: | IRQ15 <sup>2)</sup> | disabled <sup>3)</sup> |

| Primary EIDE channel:   | IRQ14 <sup>2)</sup> | IRQ14 <sup>2)</sup>    |

| PS/2 mouse:             | IRQ12 <sup>1)</sup> | IRQ12 <sup>1)</sup>    |

| USB interface:          | IRQ11 <sup>1)</sup> | IRQ15 <sup>1)</sup>    |

| LAN interface:          | IRQ11 <sup>1)</sup> | IRQ15 <sup>1)</sup>    |

| On-board LPT:           | IRQ11 <sup>1)</sup> | IRQ15 <sup>1)</sup>    |

| Floppy disk controller: | IRQ 6               | disabled <sup>3)</sup> |

| AGP controller:         | -                   | -                      |

| On-board COM A:         | IRQ4 <sup>1)</sup>  | IRQ4 <sup>1)</sup>     |

| On-board COM B:         | IRQ3 <sup>1)</sup>  | IRQ3 <sup>1)</sup>     |

1) Free for the SMP16 bus if disabled in BIOS Setup (see there)

2) Available for the SMP-INT depending on the enabled IDE channel

3) Channel deactivated to prevent hardware damage if wrong 64-bit CPCI backplane is used

#### Attention:

Starting with BIOS versions 1.03 or 2.03 (for upper levels KS01 or KS1x/KS02 of the SMP16-CPU065), the IRQ for LAN and USB can be deactivated in BIOS Setup. Automatic routing for the PCI bus starts at IRQ15 (if free).

IRQ14 and IRQ9 are excluded from the automatic interrupt routing for the PCI bus.

The PCI bus has four INT lines (INTA to INTD). BIOS routes these to up to four PC IRQs. With a maximum of four slots on the IPCI bus and the PCI devices on board, this means that several devices must share an interrupt. PCI device drivers support this, and BIOS switches these IRQs from edge-triggered to level-triggered (see chapter 7.2).

#### Attention:

Currently, RMOS does not support level-triggered interrupts.

|                               | intc1                                                         | intc2                                                                               | Block Conne                                 | ection Use                                                                                                                | Interrupt-<br>Vector <sup>2)</sup> |

|-------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                               | irq0 _                                                        |                                                                                     |                                             | (Counter 0)                                                                                                               | 08H                                |

|                               | irq1                                                          |                                                                                     | — IRQ1                                      | — (Keyboard)                                                                                                              | 09H                                |

|                               | irq2 _                                                        |                                                                                     |                                             | (Cascading)                                                                                                               | 0AH                                |

|                               |                                                               | irq0 —                                                                              |                                             | — (First realtime clock)                                                                                                  | 70H                                |

|                               |                                                               | irq1 —                                                                              | — IRQ9                                      |                                                                                                                           | 71H                                |

|                               |                                                               | irq2 —                                                                              | — IRQ10                                     | SMP16 bus: c25 <sup>3)</sup>                                                                                              | 72H                                |

|                               |                                                               | irq3 —                                                                              | — IRQ11                                     |                                                                                                                           | 73H                                |

|                               |                                                               | irq4 —                                                                              | — IRQ12                                     | (PS2 mouse) <sup>4)</sup> and SMP16 I                                                                                     | ous: c29 <sup>3)</sup> 74H         |

|                               |                                                               | irq5 —                                                                              |                                             | (error coprozessor)                                                                                                       | 75H                                |

|                               |                                                               | irq6 —                                                                              | — IRQ14                                     | — Hard disk, primary EIDE cha                                                                                             | nnel <sup>1)</sup> 76H             |

|                               |                                                               | irq7 —                                                                              | — IRQ15                                     | — Hard disk, secondary EIDE of                                                                                            | channel <sup>1)</sup> 77H          |

|                               | irq3                                                          |                                                                                     | IRQ3                                        | — (COM B) $^{\scriptscriptstyle 5)}$ and SMP16 bus:                                                                       | c15 <sup>3)</sup> 0BH              |

|                               | irq4 —                                                        |                                                                                     | — IRQ4                                      | — (COM A) $^{\scriptscriptstyle 5)}$ and SMP16 bus:                                                                       | c17 0CH                            |

|                               | irq5 —                                                        |                                                                                     | — IRQ5                                      | — SMP16 bus: c19 <sup>3)</sup>                                                                                            | 0DH                                |

|                               | irq6 🗕                                                        |                                                                                     | — IRQ6                                      | — (Floppy disk)                                                                                                           | 0EH                                |

|                               | irq7 _                                                        |                                                                                     | — IRQ7                                      | (LPT1) <sup>6)</sup> and SMP16 bus: c2                                                                                    | 21 <sup>3)</sup> 0FH               |

| ntc1,<br>ntc2<br>() =<br>1) = | With "in<br>Board of<br>Signal<br>depend<br>signal I<br>SMP16 | nterfaces"<br>or block int<br>IRQ* of the<br>ding on the<br>RQ* is not<br>blus must | IDE channel<br>available as<br>then be used | t inputs<br>us is fed in via IRQ14 or IRQ15,<br>used. If both IDE channels are use<br>an interrupt input. Another IRQx* c |                                    |

| 2) =                          | Applies                                                       | to MS-DC                                                                            | DS only                                     |                                                                                                                           |                                    |

| 3) =                          | Additio                                                       | nal interru                                                                         | ot controller ca                            | an be included via interrupt matrix (                                                                                     | see chapter 2.4.5                  |

| 4) =                          | If PS2                                                        | mouse ena                                                                           | abled in Setup                              | )                                                                                                                         |                                    |

| 5) =                          | If COM                                                        | enabled i                                                                           | n Setup                                     |                                                                                                                           |                                    |

|                               |                                                               | enabled in                                                                          | Cotup                                       |                                                                                                                           |                                    |

| 6) =                          | ILPI                                                          | enableu in                                                                          | Setup                                       |                                                                                                                           |                                    |

Figure 4.2 Internal circuiting of the interrupt controller (no PCI device included)

### SMP16 interrupts

#### Note:

The LAN controller can be disabled in BIOS (see chapter 8.1.9).

Interrupts IRQ3, IRQ4, IRQ7 and IRQ12 are used by internal components (COM B, COM A or LPT1, PS2 mouse).

| COM A or COM B | • | On board, active ("enable" in BIOS Setup)<br>IRQ4/IRQ3 are assigned.<br>SMP16-IRQ can't get through. |

|----------------|---|------------------------------------------------------------------------------------------------------|

| LPT1           | • | On board, active ("enable" in BIOS Setup)<br>IRQ7/IRQassigned.<br>SMP16-IRQ can't get through.       |

| PS2 mouse      | • | On board, active ("enable" in BIOS Setup)<br>IRQ12/IRQ assigned.<br>SMP16-IRQ can't get through.     |

#### Attention:

When "ACPI Function" is enabled in Setup (see chapter 9.1.6), IRQ9 is used by the ACPI function and is no longer available on the SMP16 bus.

#### Note:

If the extra interrupt controller is used (see chapter 4.7.2), its interrupt output can be routed to one of the SMP interrupts (see chapter 7.2.1.7). This interrupt output is then no longer available on the SMP16 bus.

Use of the extra interrupt controller provides five additional interrupts (DREQx\* signals of the SMP16 bus). The additional interrupts are handled as described in chapter 7.2.1.1.

#### 4.3.6 NMI Generation

The NMI logic is controlled in 2 registers (see chapter 7.2.1).

Register 61h

| NMI status information |                               |                         |  |  |  |  |  |

|------------------------|-------------------------------|-------------------------|--|--|--|--|--|

| Bit 7:                 | SERR# of the I                | PCI bus                 |  |  |  |  |  |

| Bit 6:                 | Bit 6: IOCHCK# of the ISA bus |                         |  |  |  |  |  |

| NMI enable             |                               |                         |  |  |  |  |  |

| Bit 3:                 | IOCHCK#                       | 0 = enable, 1 = disable |  |  |  |  |  |

| Bit 2:                 | SERR#                         | 0 = enable, 1 = disable |  |  |  |  |  |

Register 70h

Bit 7: General NMI enable

- 0 = enabled

- 1 = disabled

## 4.3.7 Bus Timing

BIOS sets the board to the optimum speed for memory and bus accesses. The ISA bus which is clockpulsed with 8.33 MHz is the basis of SMP16 bus timing.

Timing of the PC-AT-compatible CPU boards is based on the ISA specification IEEE-P996 (draft).

With 16-bit accesses, the I/O must return the RDYIN signal within a maximum of 82 nsec (77 nsec on the SMP16 bus due to additional decoding and bus driver) after the activated command so that wait cycle are inserted.

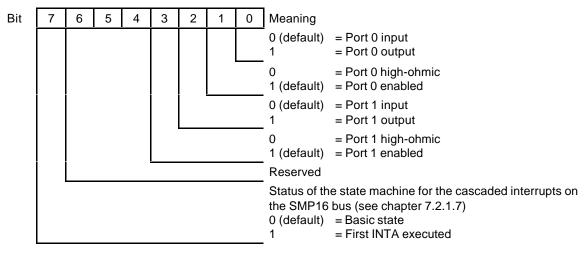

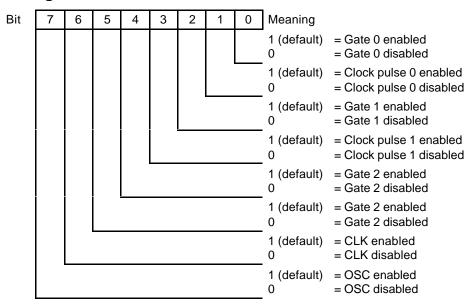

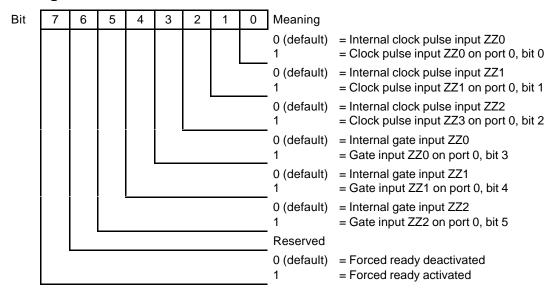

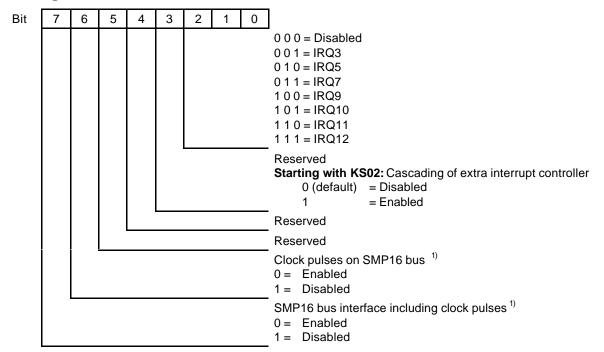

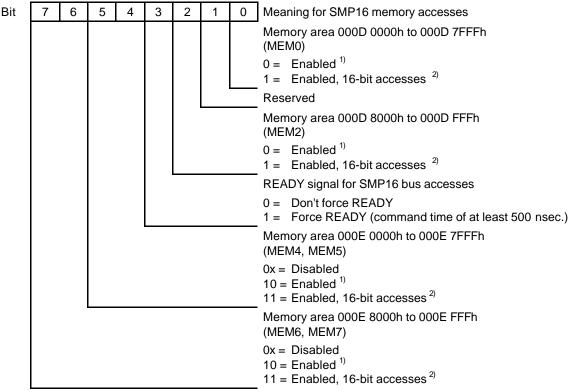

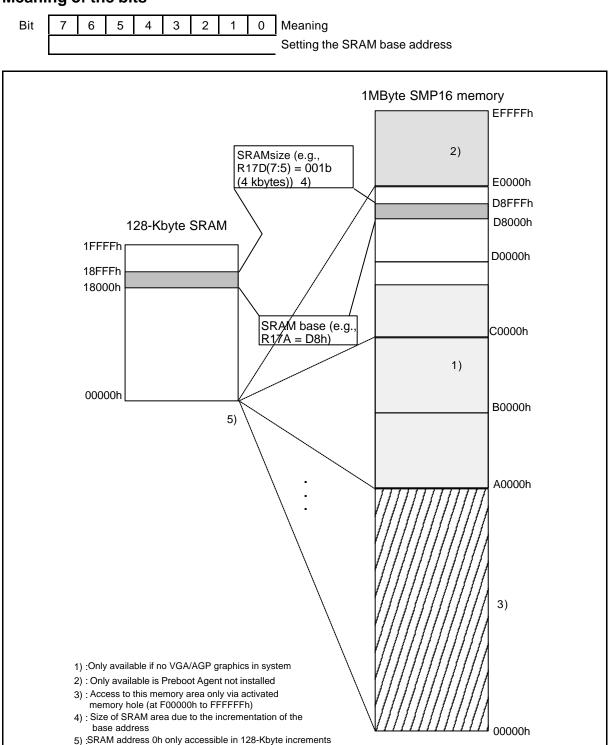

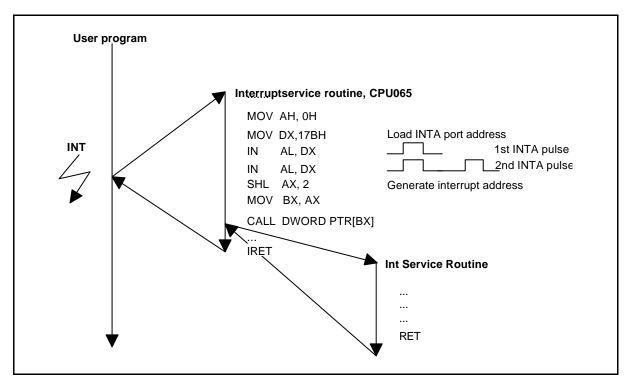

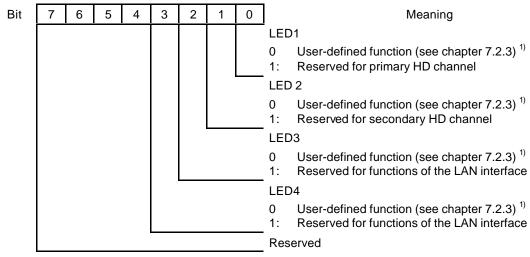

The SMP16 specifications state the time as a maximum of 100 nsec. A "Not Ready" can be set to ensure this maximum time (see chapter 7.2.1.6). Boards with the ASBIC to the SMP16 bus interface do not have critical time problems.